3.2、存储器芯片的输入与输出信号元件介绍

Q: 存储器芯片的输入与输出信号元件有哪些?

A: 存储器芯片的输入与输出信号元件包括地址 (Address)、数据 (Data)、WE(write)、WR(read) 和 CS(chip select)。

Q: WE 信号的作用是什么?

A: WE 信号表示写使能信号,高电平表示写数据,低电平表示读数据。

Q: CS 信号的作用是什么?

A: CS 信号表示片选信号,用于选择要访问的存储芯片。

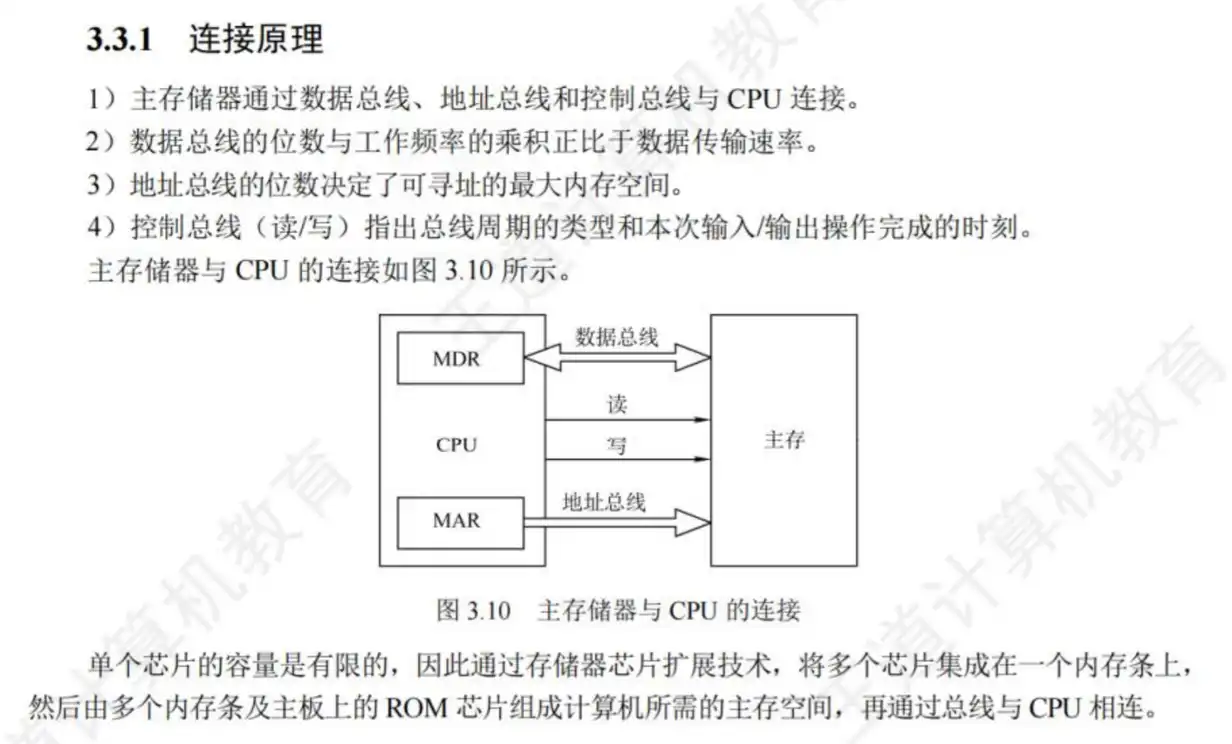

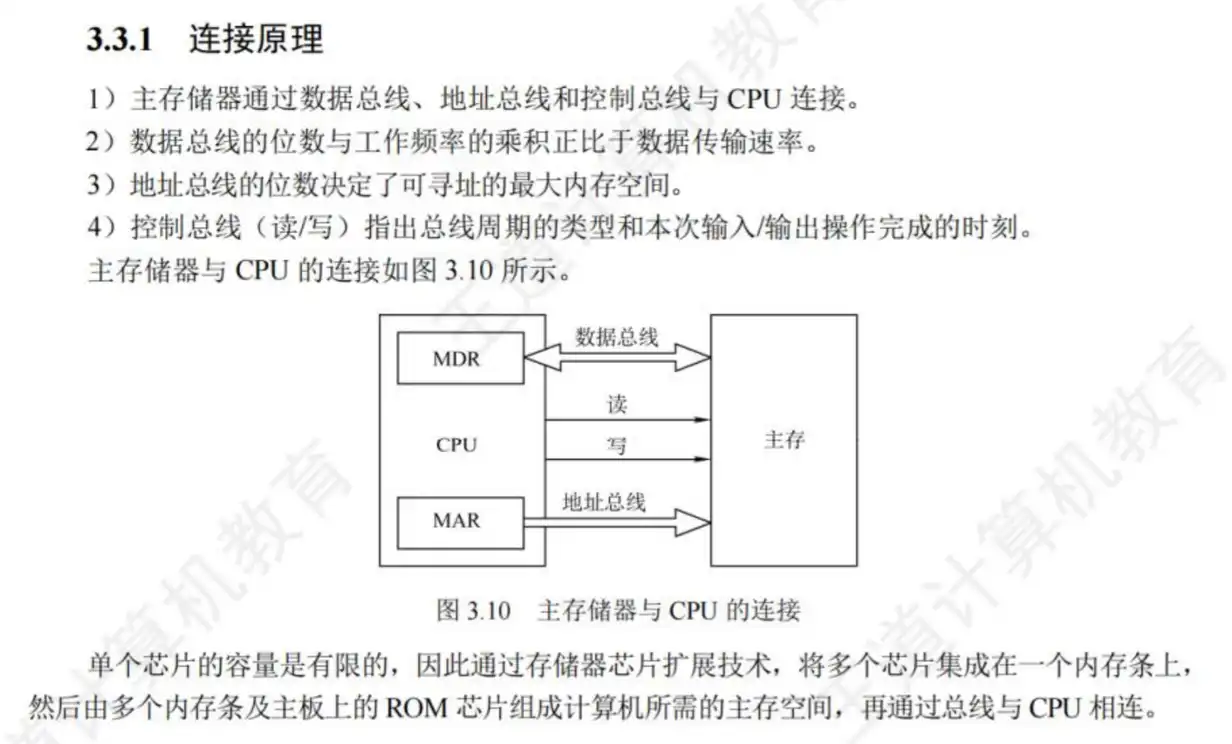

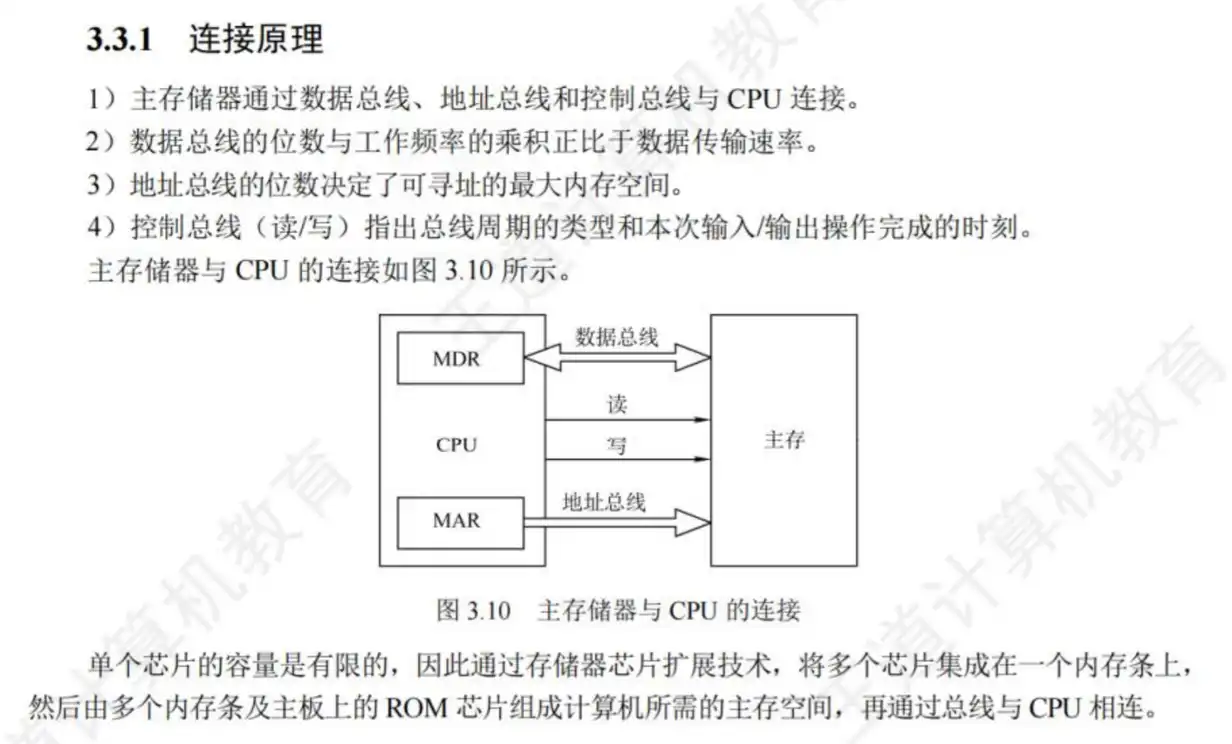

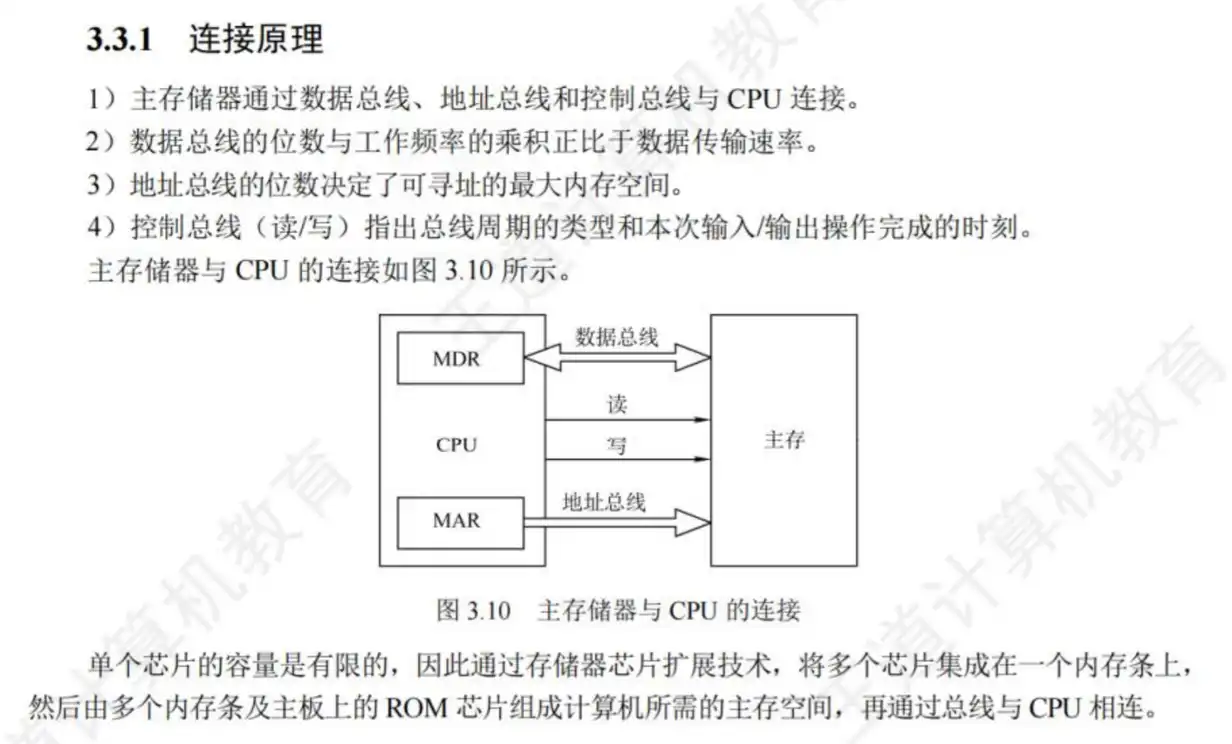

3.3.1 连接原理

Q: 主存储器如何与 CPU 连接?

A: 主存储器通过数据总线、地址总线和控制总线与 CPU 连接。

Q: 数据总线的位数决定了什么?

A: 数据总线的位数与工作频率的乘积正比于数据传输速率。

Q: 地址总线的位数决定了什么?

A: 地址总线的位数决定了可寻址的最大内存空间。

Q: 控制总线的作用是什么?

A: 控制总线指出总线周期的类型和本次输入/输出操作完成的时刻。

3.3.2 主存容量的扩展

Q: 为什么要扩展主存容量?

A: 由于单个存储芯片的容量是有限的,它在字数或字长方面与实际存储器的要求都有差距,因此需要在字和位两方面进行扩充才能满足实际存储器的容量要求。

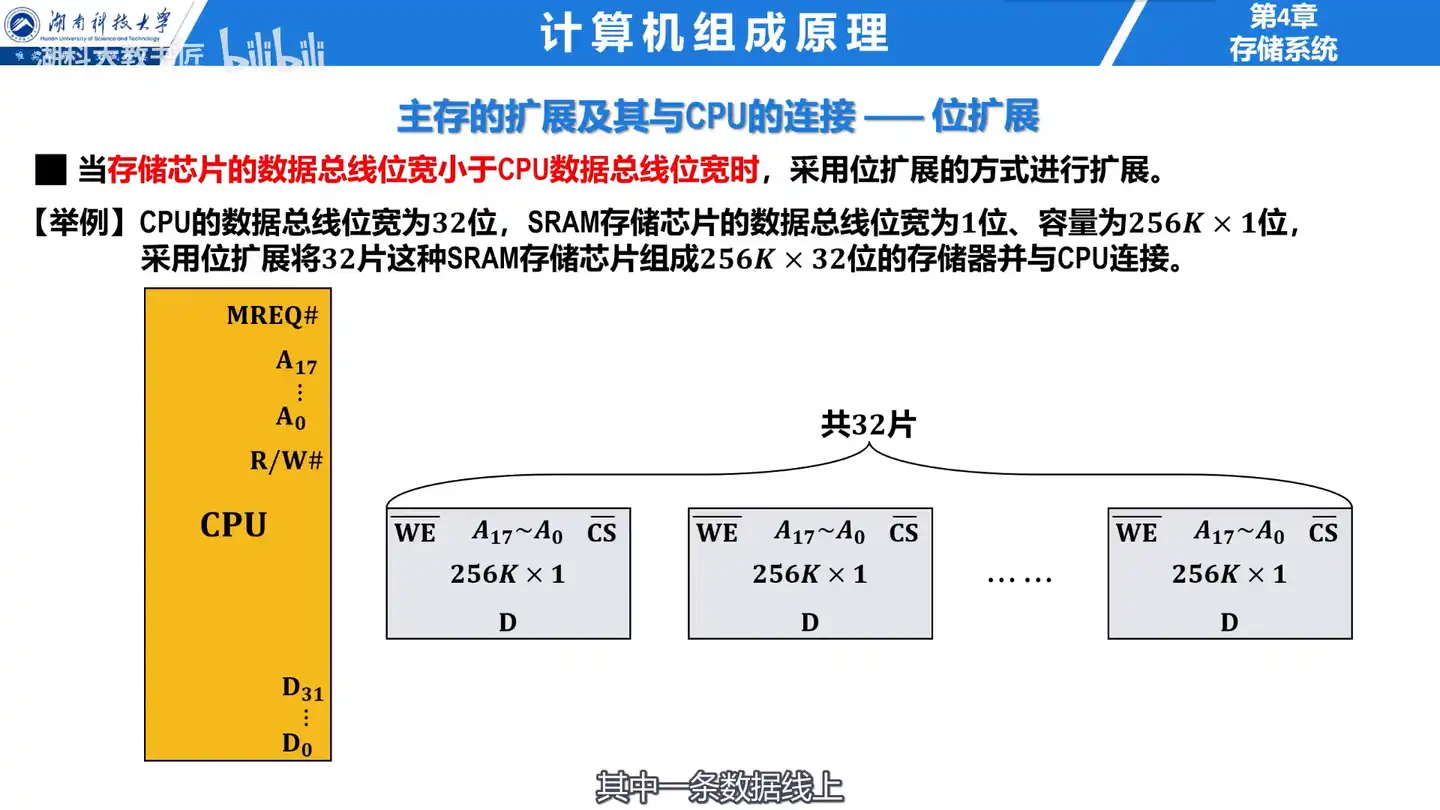

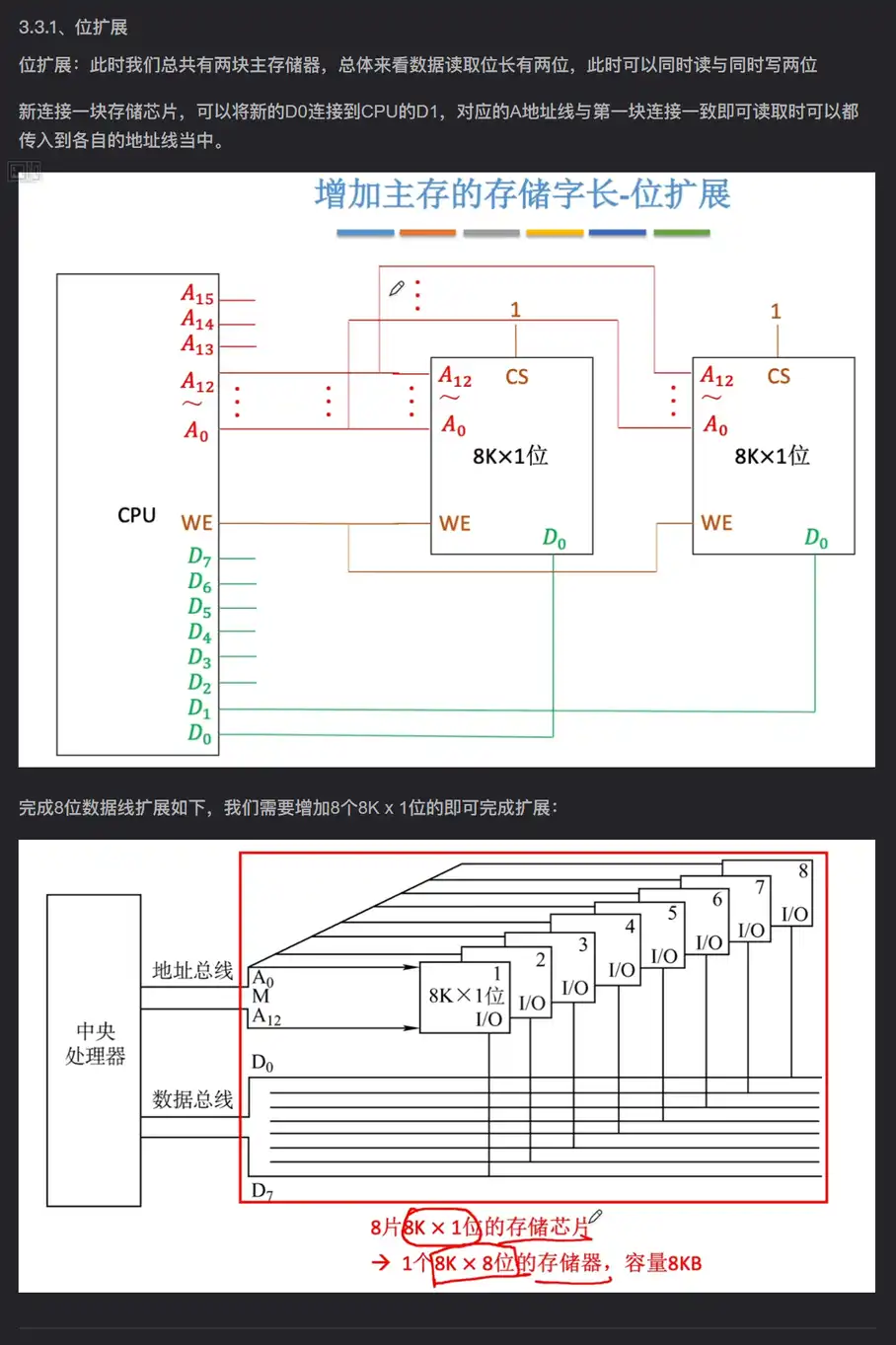

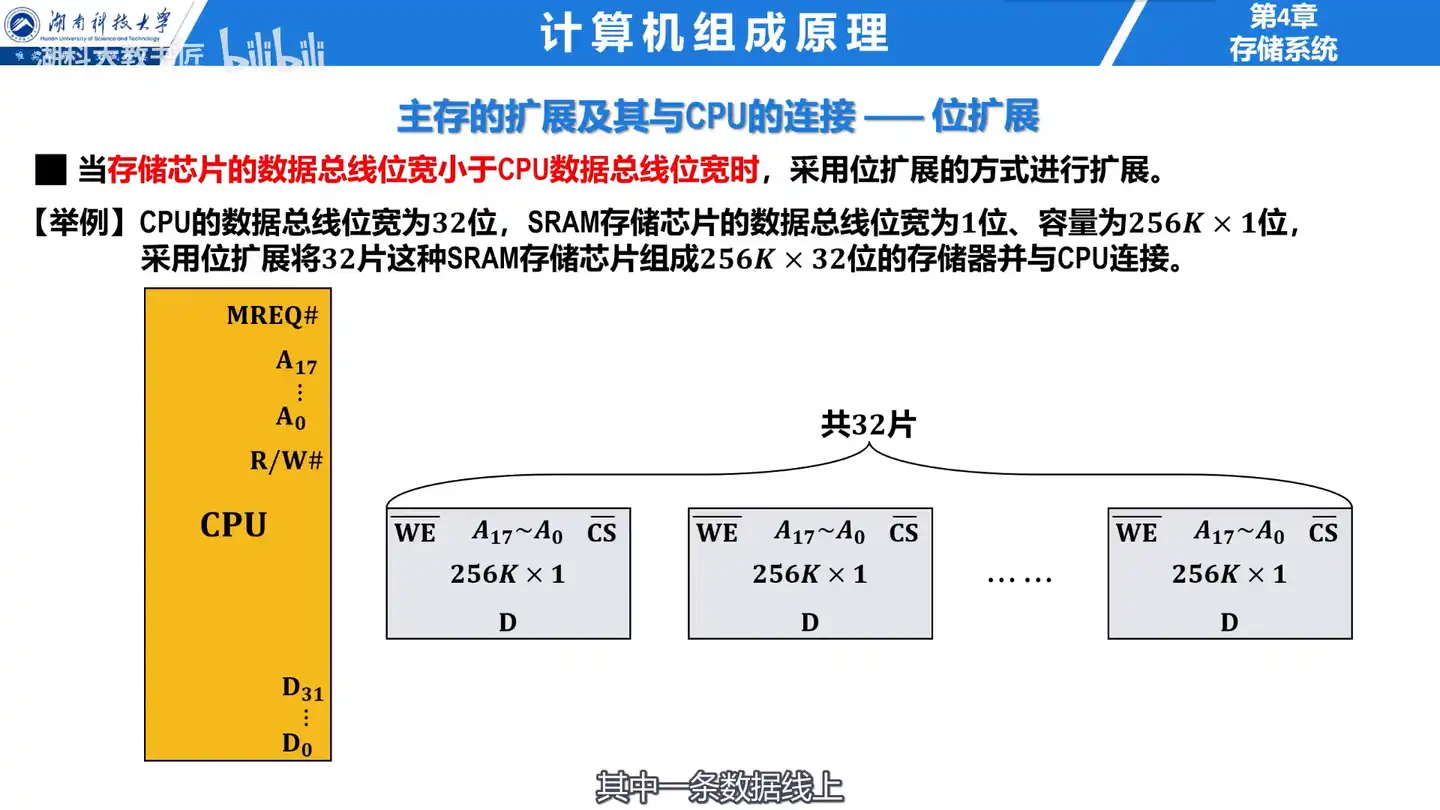

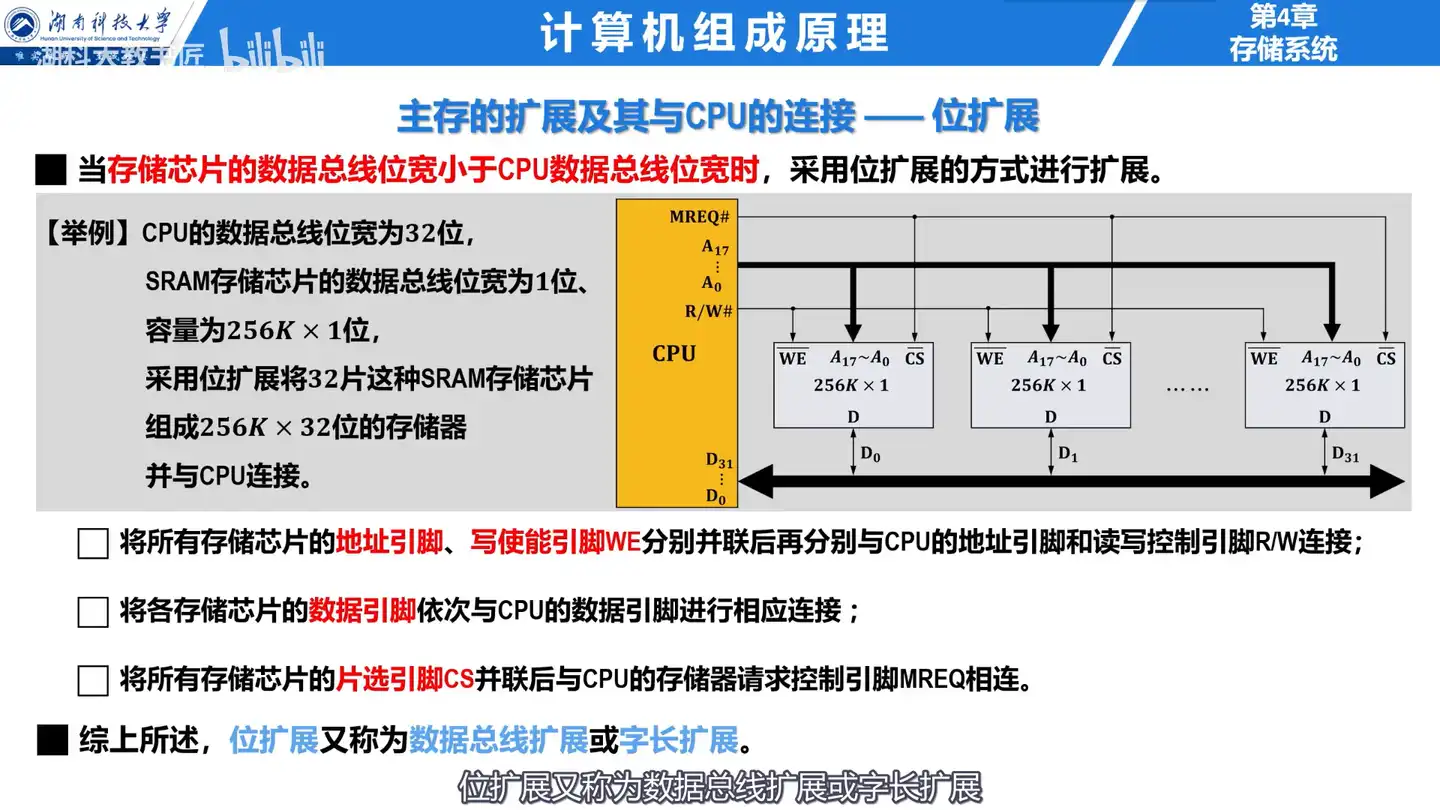

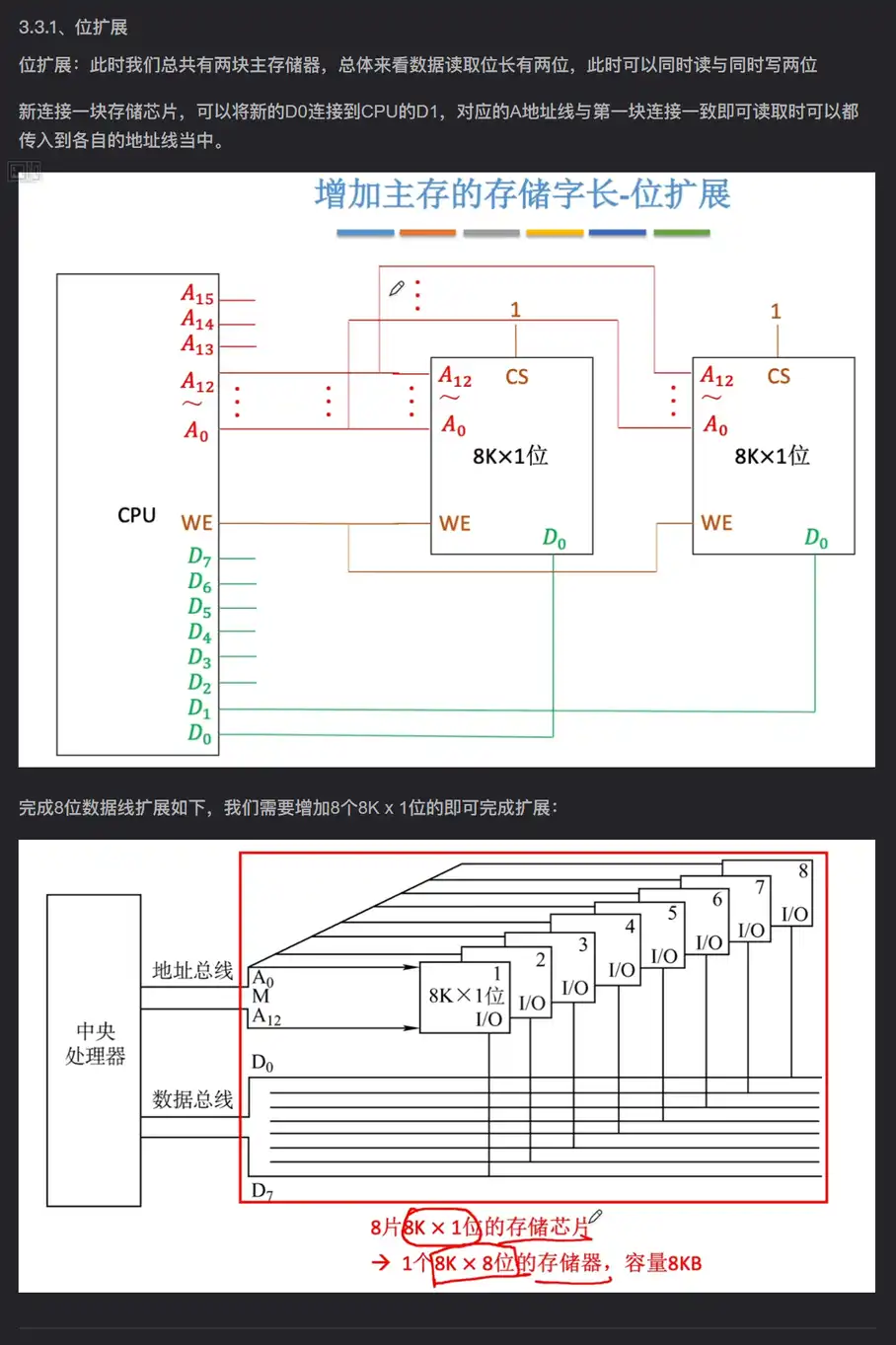

1. 位扩展法

Q: 位扩展法的目的是什么?

A: 位扩展法的目的是对字长进行扩展 (增加存储字长)。

位宽不一致时使用,这里就是32位的地址线,要想每根线都插上东西,但是每个芯片只有一个口给插,所以要32个芯片来让cpu上面的32条数据线可以都插齐(数据线就是下面这个D0到D12)

Q: 位扩展法的连接方式是什么?

A: 各芯片的地址线、片选线和读/写控制线与系统总线相应并联;

各芯片的数据线单独引出, 分别连接系统数据线。

- 将多块存储芯片的数据线连接到 CPU 的数据总线。

- 将各芯片的地址线、片选线和读/写控制线与系统总线相应并联。

Q: 位扩展法的特点是什么?

A: 各芯片同时工作。

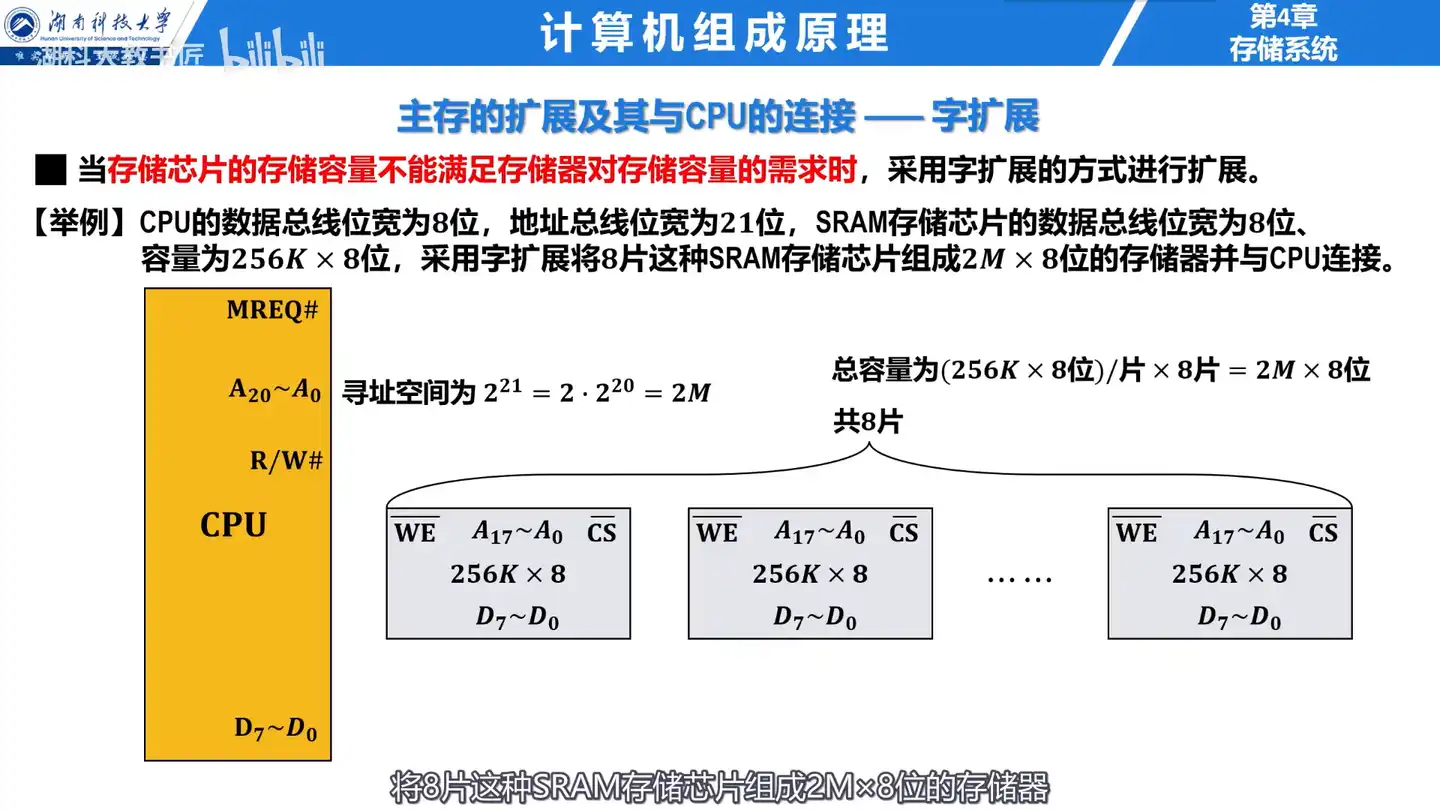

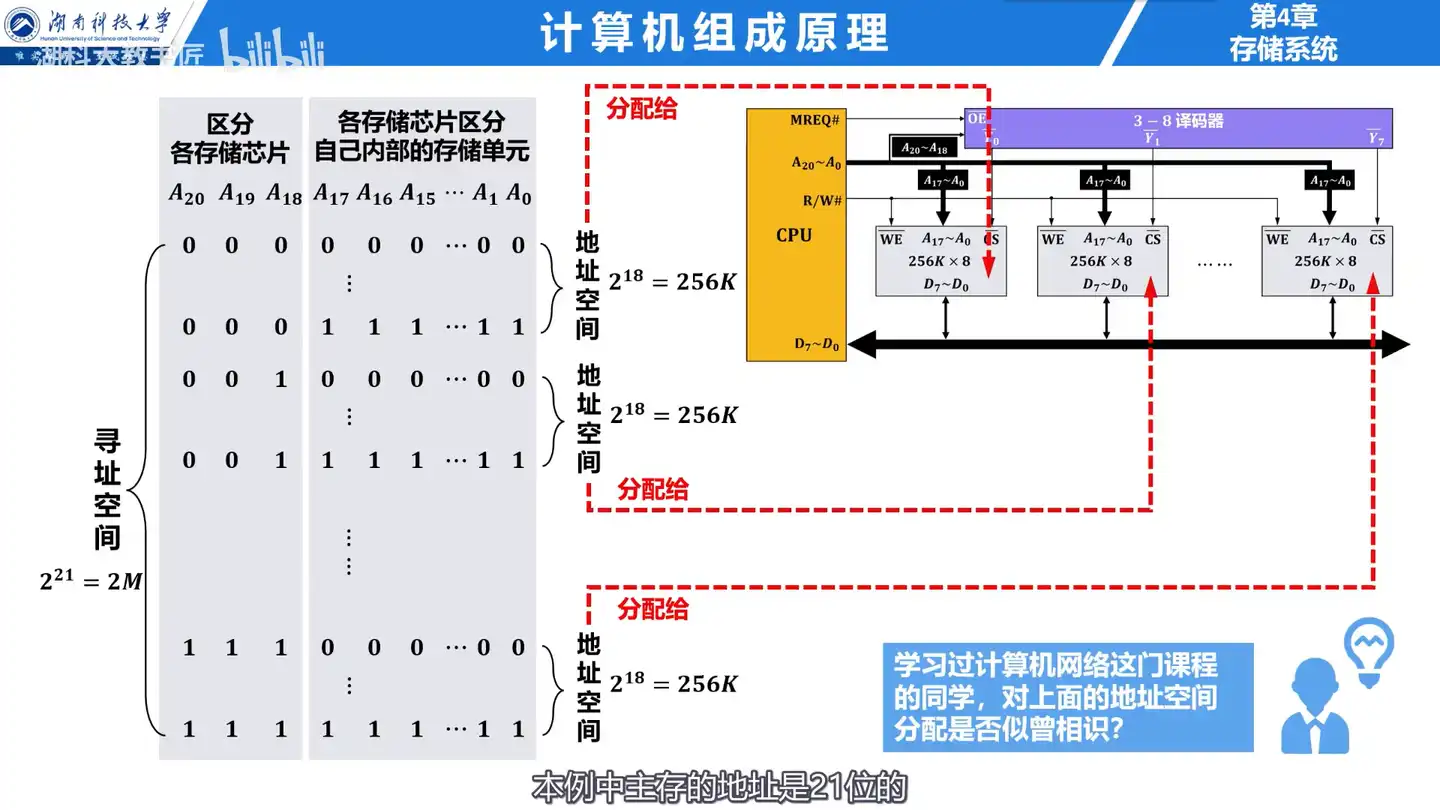

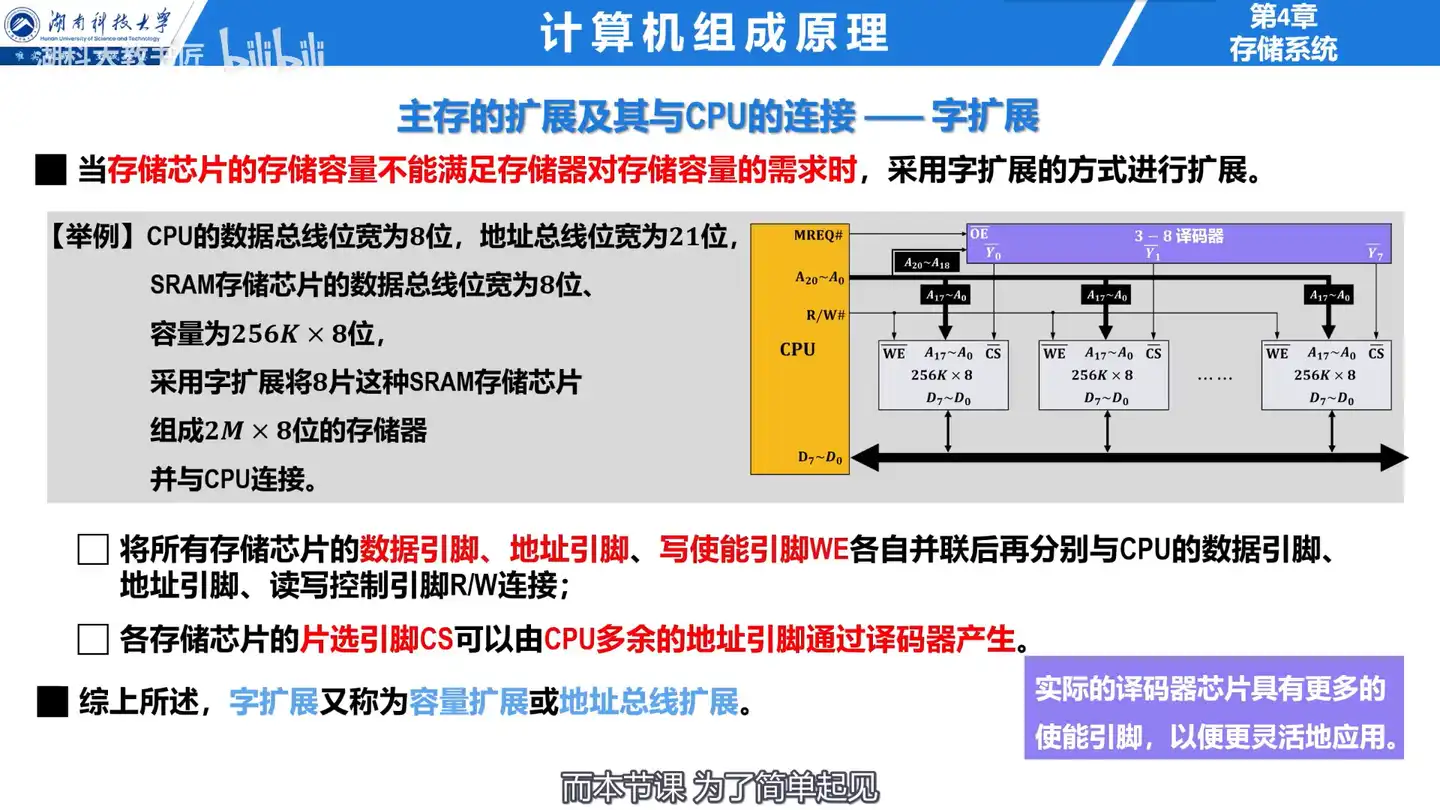

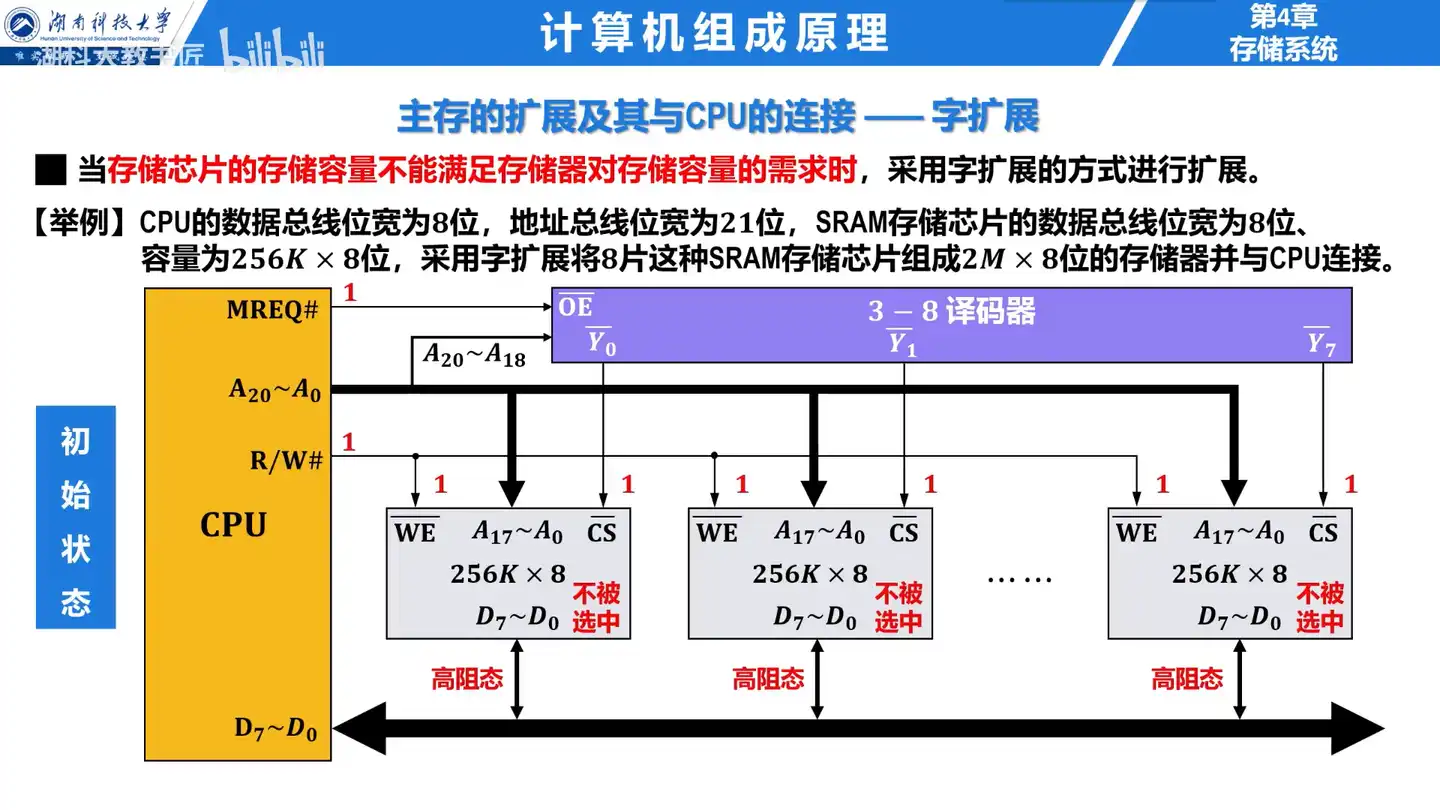

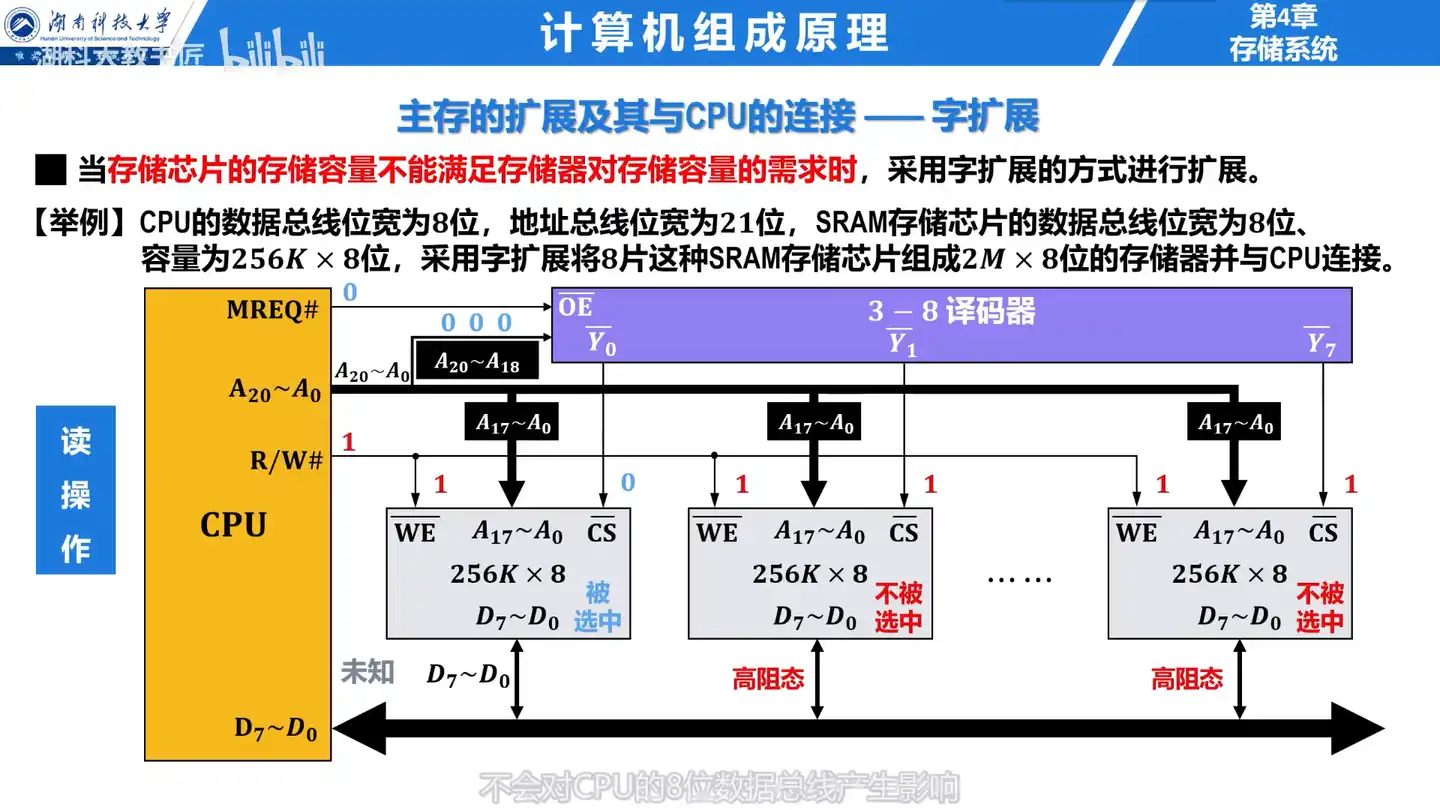

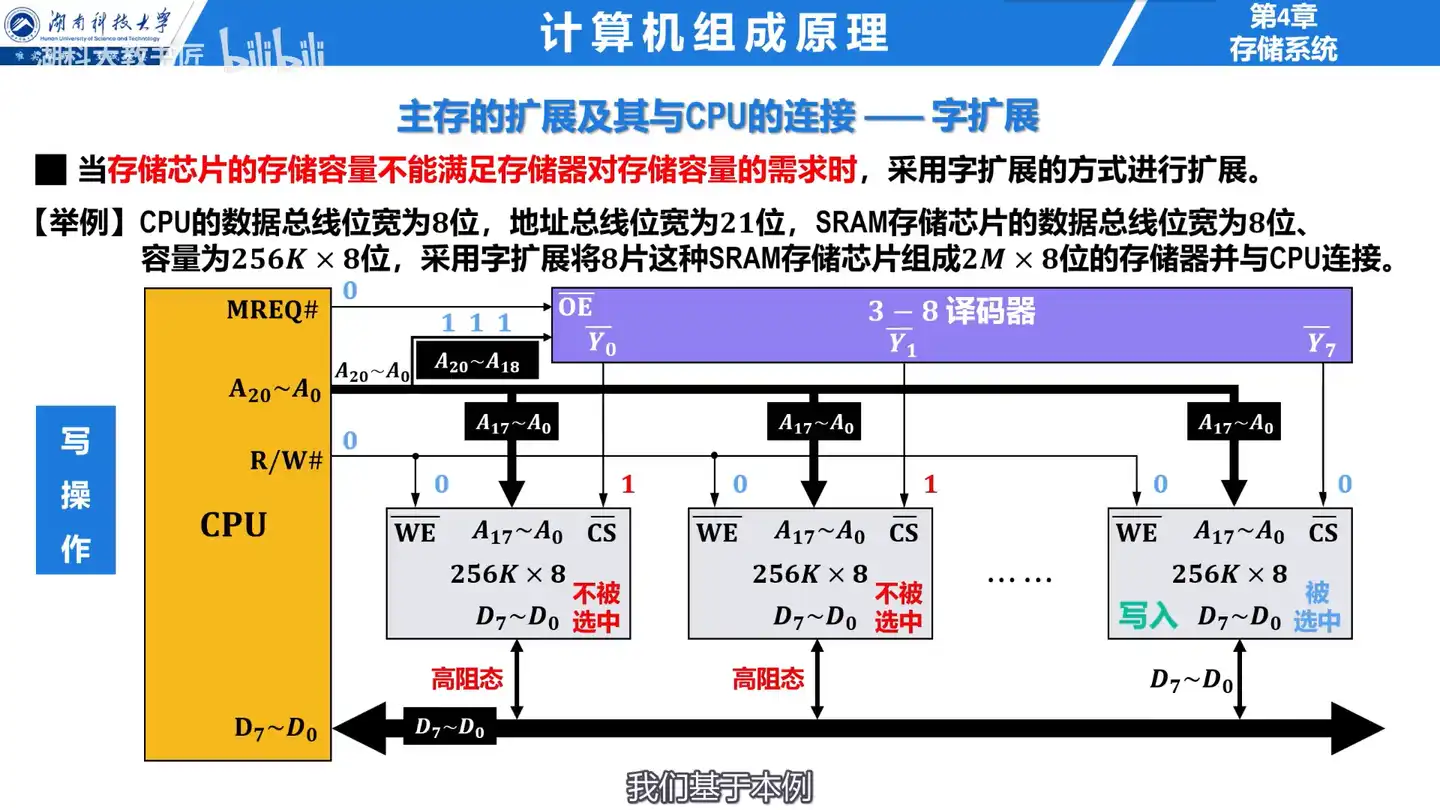

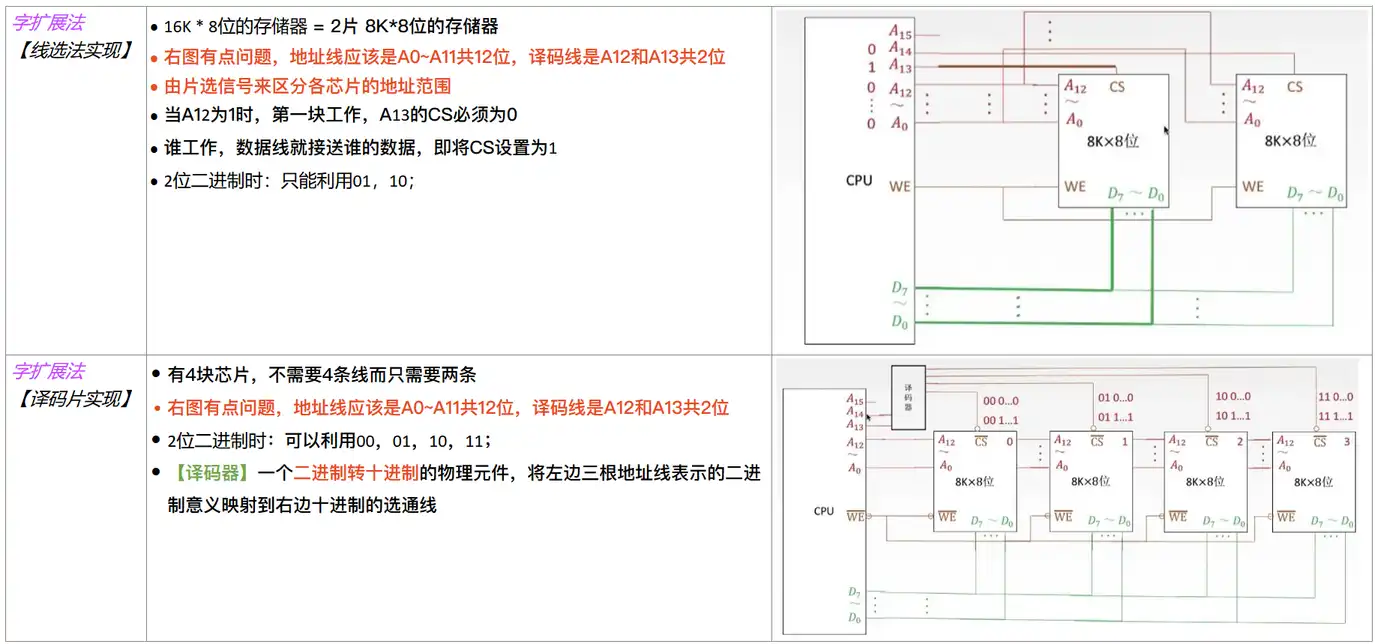

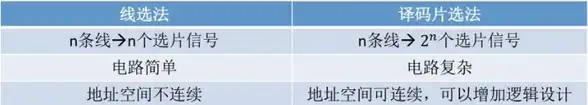

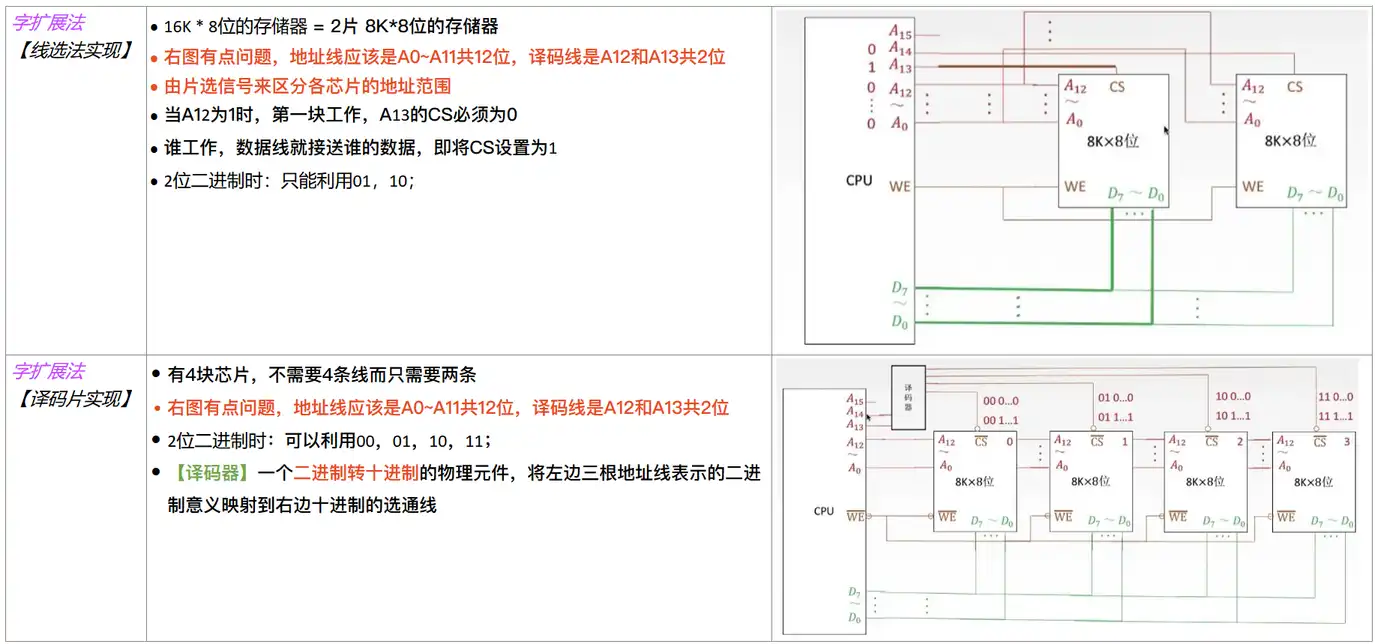

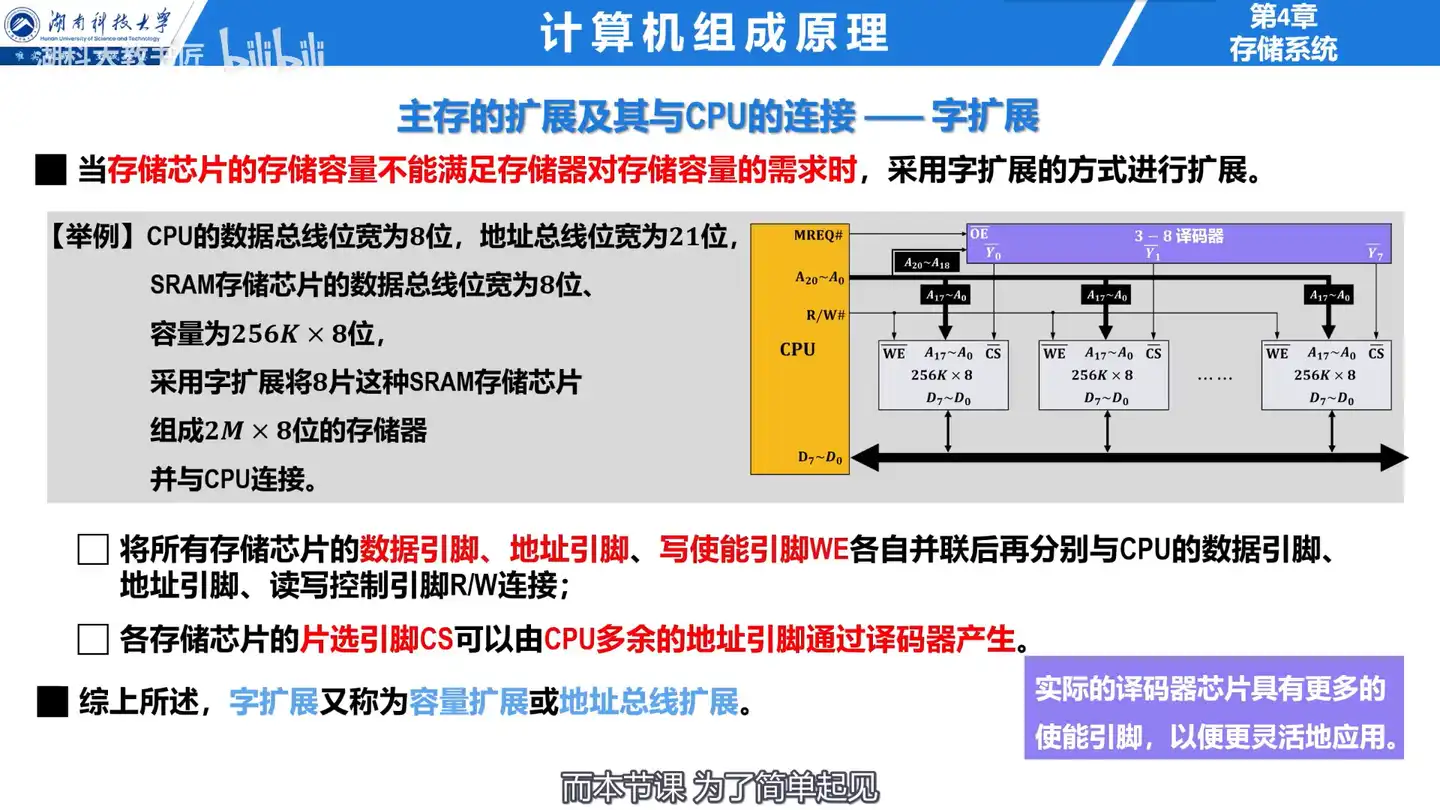

2. 字扩展法

Q: 字扩展法的目的是什么?

A: 字扩展法的目的是对存储字的数量进行扩展。

容量不一致时使用

和CIDER非常类似,划分子网的意思,接线口的位宽是对齐的,也就是CPU有21条线远远多余芯片上要插的8条线,但是两者容量不匹配,所以就把cpu多的线拿出来,接入更多的芯片,用多的线作为子网号来控制每次读取写入哪个芯片

Q: 字扩展法的连接方式是什么?

A: 各芯片的地址线与系统地址线的低位对应相连; 芯片的数据线和读/写控制线与系统总线相应并联; 由系统地址线的高位译码得到各芯片的片选信号。

- 将各芯片的地址线与系统地址线的低位对应相连。

- 将芯片的数据线和读/写控制线与系统总线相应并联。

- 由系统地址线的高位译码得到各芯片的片选信号。

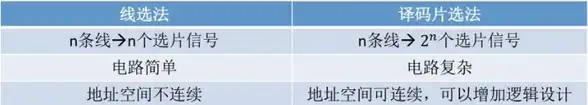

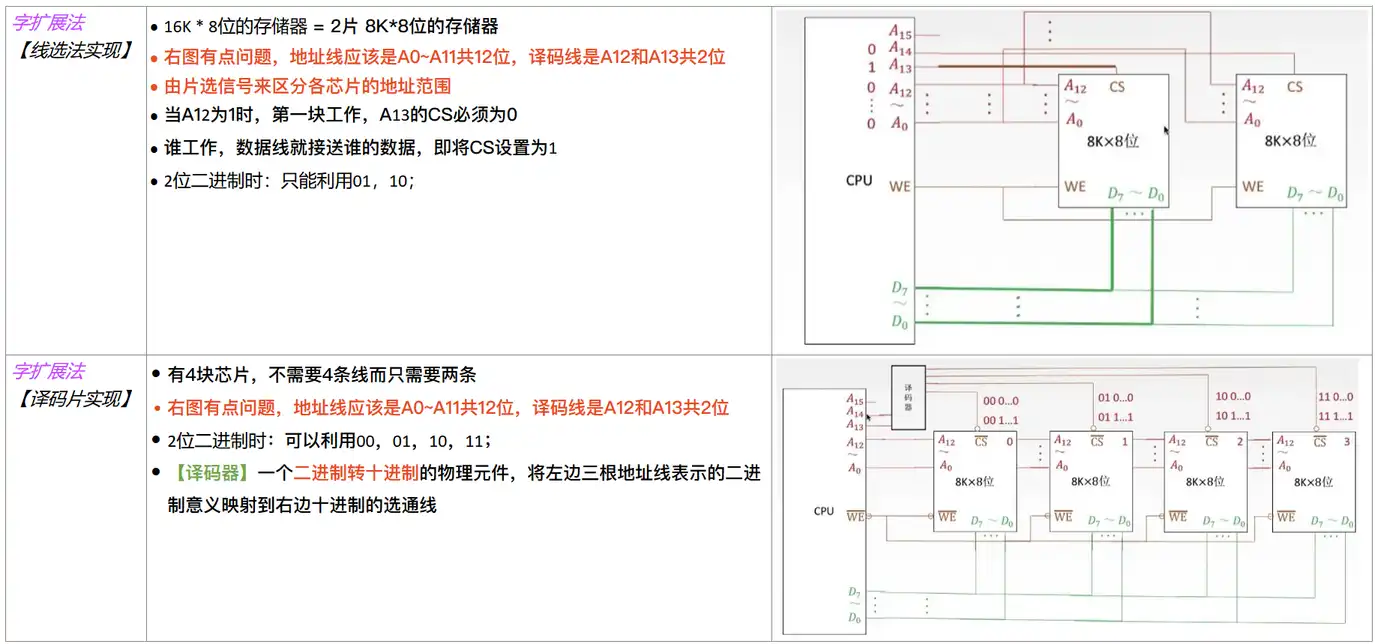

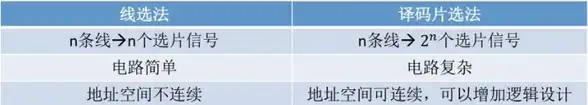

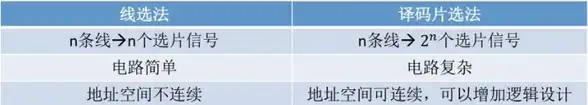

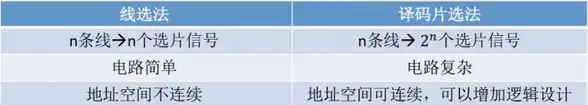

Q: 字扩展的两种方法是什么?

A: - 线选法

- 译码片选法

两者的区别在于存储器和cpu需要相连的线的根数不同

Q:什么是线选法?

A:

直接用地址线裸连

Q:什么是译码片选法?

A:

通过地址线扩展,搭配译码器

Q: 字扩展法的特点是什么?

A: 各芯片分时工作。

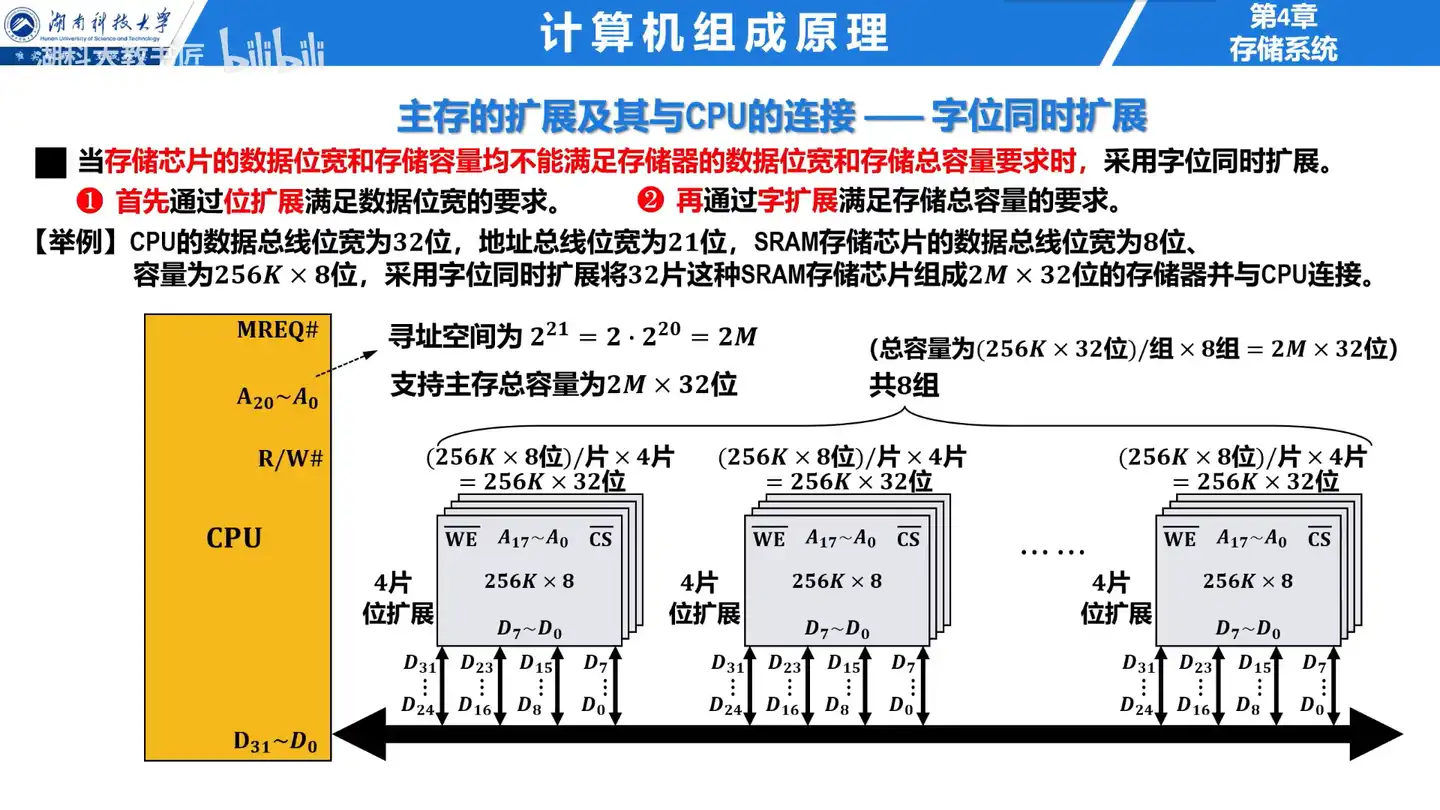

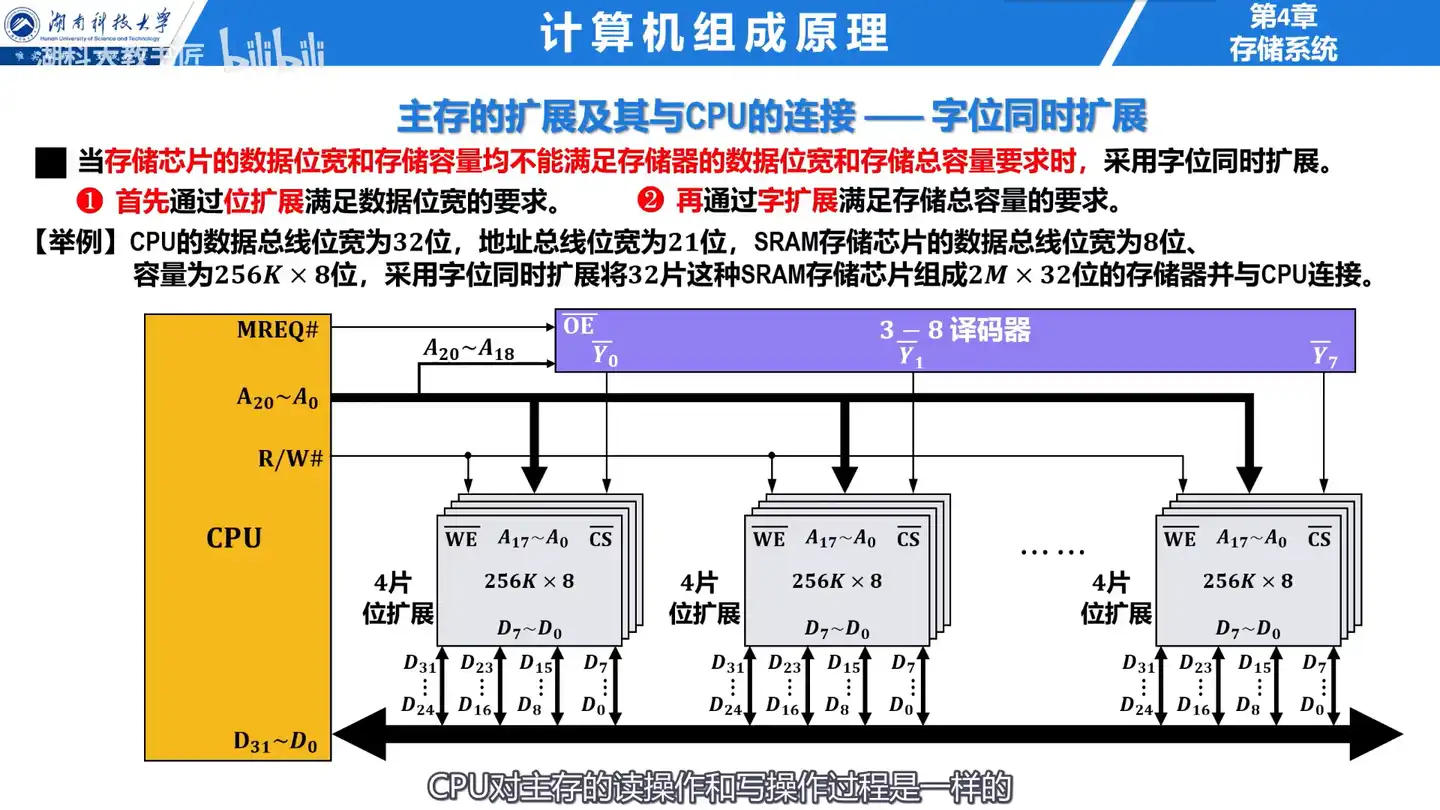

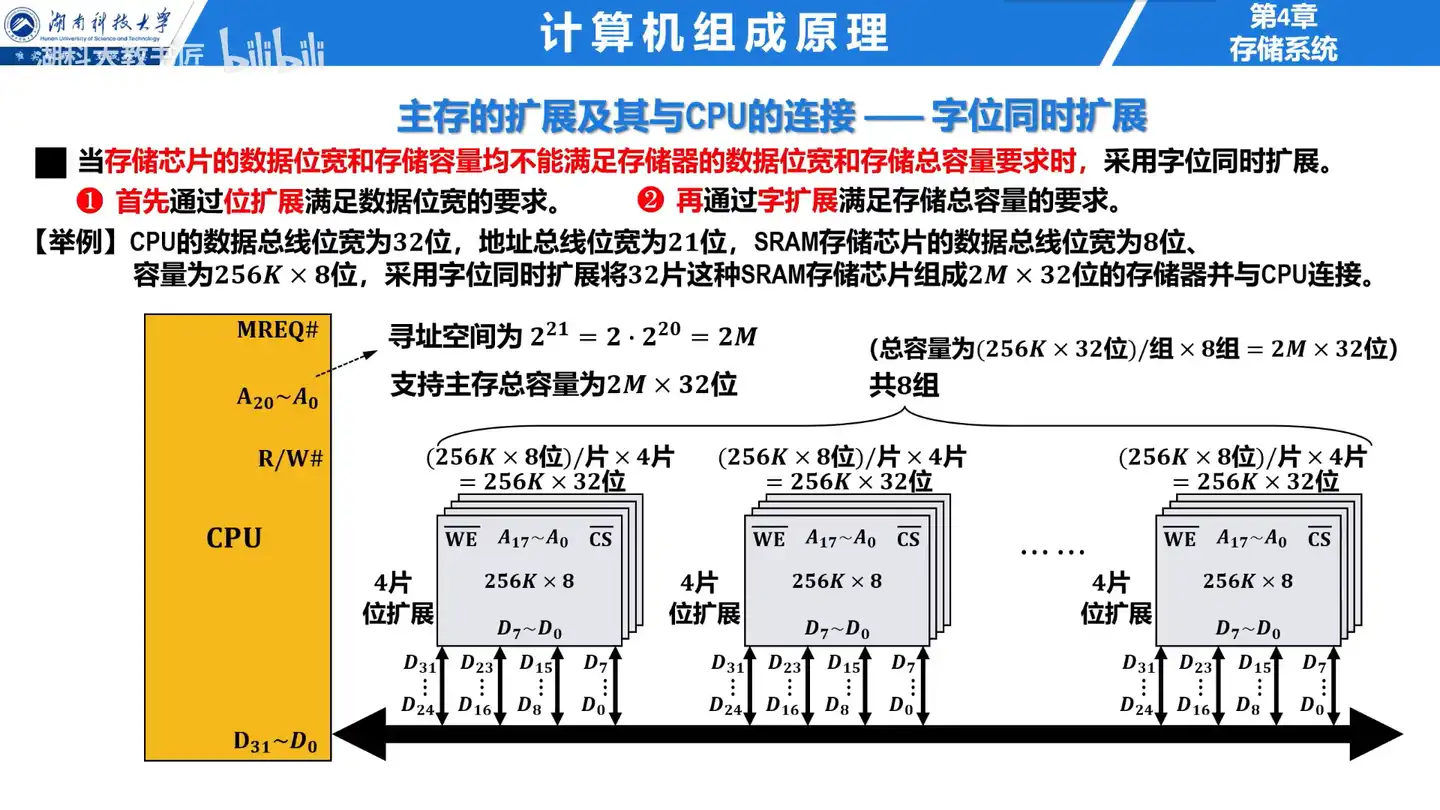

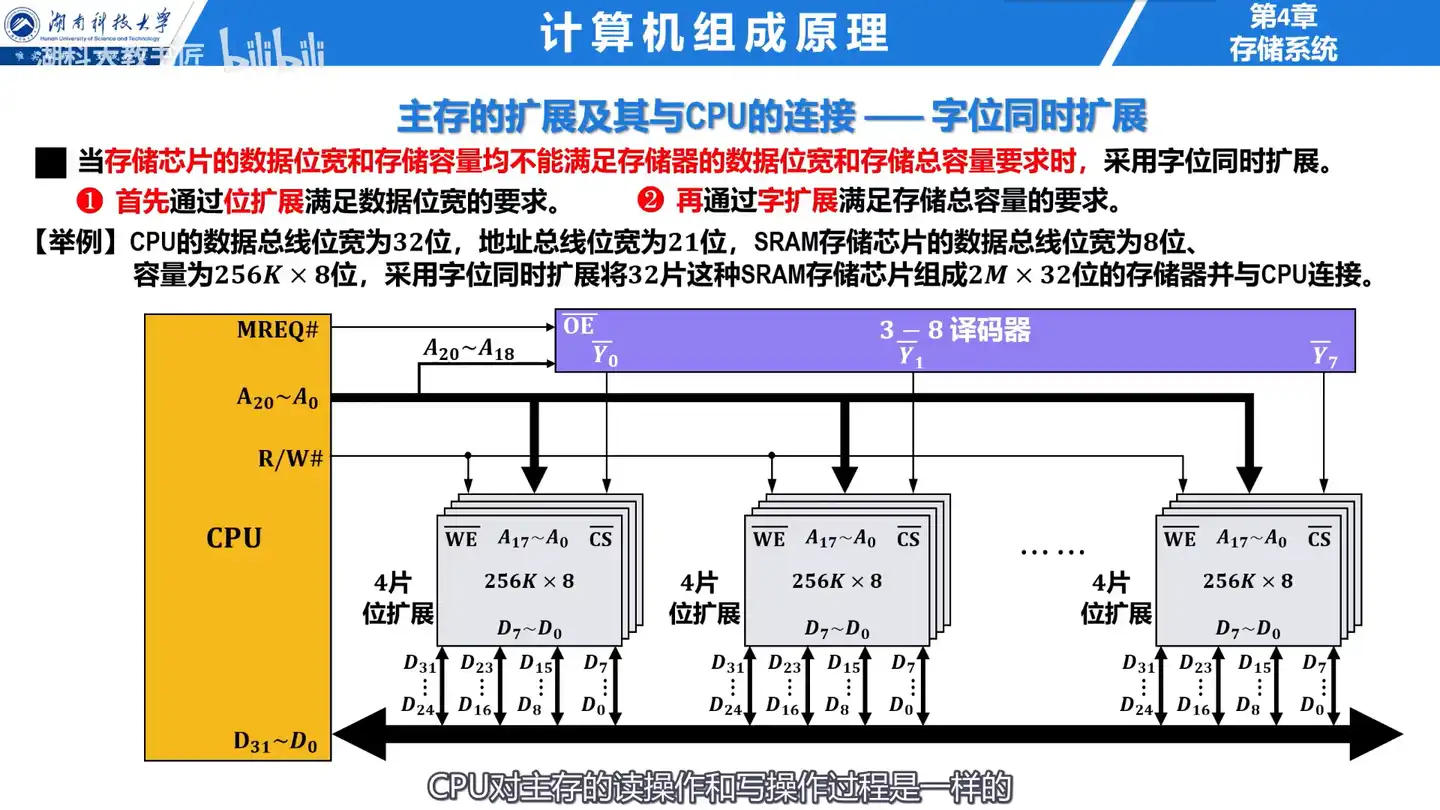

3. 字位同时扩展法

Q: 字位同时扩展法的目的是什么?

A: 字位同时扩展法的目的是既增加存储字的数量,又增加存储字长。

读写操作和字扩展状态下的读写操作是一样的

Q: 字位同时扩展法的连接方式是什么?

A: 将进行位扩展的芯片作为一组, 各组的连接方式与位扩展的相同; 由系统地址线高位译码产生若干片选信号, 分别接到各组芯片的片选信号。

- 将进行位扩展的芯片作为一组。

- 各组的连接方式与位扩展的相同。

- 由系统地址线高位译码产生若干片选信号,分别接到各组芯片的片选信号。

Q: 字位同时扩展法的特点是什么?

A: 各组芯片分时工作。

补充:译码器

Q: 译码器的作用是什么?

A: 译码器将 CPU 送出的地址信号转换成片选信号,用于选择要访问的存储芯片。

Q: 译码器是如何工作的?

A: 译码器根据 CPU 送出的地址信号,选择对应的输出端,该输出端对应一个存储芯片的片选信号。

Q: 译码器的类型有哪些?

A: - 1-2 译码器

- 2-4 译码器

- 3-8 译码器

Q: 译码器如何连接到存储芯片?

A: 译码器的输出端连接到存储芯片的片选信号端。

3.3.3 存储芯片的地址分配和片选

Q: CPU 如何访问存储单元?

A: CPU 首先要选择存储芯片(片选),然后在选定的芯片中选择具体的存储单元(字选)。

Q: 片选信号的产生方法有哪些?

A:

- 线选法

- 译码片选法

1. 线选法

Q: 线选法的特点是什么?

A: 线选法用除片内寻址外的高位地址线直接连接至各个存储芯片的片选端,当某位地址线信息为 “0” 时,就选中与之对应的存储芯片。

Q: 线选法的优点是什么?

A: 线选法不需要地址译码器,线路简单。

Q: 线选法的缺点是什么?

A: 地址空间不连续,选片的地址线必须分时为低电平,不能充分利用系统的存储器空间,造成地址资源的浪费。

2. 译码片选法

Q: 译码片选法的特点是什么?

A: 译码片选法用除片内寻址外的高位地址线通过地址译码器产生片选信号。

Q: 译码片选法的优点是什么?

A: 译码片选法可以充分利用系统的存储器空间,避免地址资源的浪费。

Q: 译码片选法的缺点是什么?

A: 译码片选法需要额外的地址译码器,线路复杂。

3.3.4 存储器与 CPU 的连接

1. 合理选择存储芯片

Q: 选择存储芯片时需要考虑哪些因素?

A: 选择存储芯片时需要考虑芯片的类型 (RAM 或 ROM) 和数量,以及连接的方便性。

Q: 通常 ROM 用于存放什么?

A: 通常 ROM 用于存放系统程序、标准子程序和各类常数。

Q: 通常 RAM 用于存放什么?

A: 通常 RAM 用于存放用户编程所需的数据。

2. 地址线的连接

Q: CPU 的地址线如何与存储芯片的地址线连接?

A: CPU 地址线的低位与存储芯片的地址线相连,用于选择芯片中的某一单元 (字选)。CPU 地址线的高位则在扩充存储芯片时使用,用来选择存储芯片 (片选)。

Q: 如何确定 CPU 地址线与存储芯片地址线的连接方式?

A:

- CPU 的低位地址线与存储芯片的地址线相连。

- CPU 的高位地址线用于片选。

3. 数据线的连接

Q: CPU 的数据线如何与存储芯片的数据线连接?

A:

- 当 CPU 的数据线数与存储芯片的数据线数相等时,可直接相连。

- 当 CPU 的数据线数与存储芯片的数据线数不相等时,必须对存储芯片扩位,使其数据位数与 CPU 的数据线数相等。

4. 读/写命令线的连接

Q: CPU 的读/写命令线如何与存储芯片的读/写控制端连接?

A:

- 当 CPU 的读/写命令线是合在一起的,通常高电平为读,低电平为写。

- 当 CPU 的读/写命令线是分开的 (读为

,写为

Q: 如果 CPU 的读/写命令线是分开的,如何连接?

A: CPU 的读命令线应与芯片的允许读控制端相连,而 CPU 的写命令线则应与芯片的允许写控制端相连。

5. 片选线的连接

Q: 片选线的连接与什么有关?

A: 片选线的连接与 CPU 的访存控制信号

Q: 片选线的连接有什么重要性?

A: 片选线的连接是 CPU 与存储芯片连接的关键,因为只有当 CPU 要求访存时,才要求选中存储芯片。

Q: 片选线的连接原理是什么?

A: 只有当 CPU 要求访存时 (

Q: 当 CPU 访问 I/O 时,MREQ‾MREQ 的状态是什么?

A: 当 CPU 访问 I/O 时,MREQ‾MREQ 为高,表示不要求存储器工作。