本讲,将介绍指令周期的相关知识。指令周期是指CPU从主存取出并执行一条指令所需的时间。对于无条件转移指令,仅包含取指阶段和执行阶段。需要指出的是,取指阶段还可能涉及到加密操作。

对于采用间接寻址方式的指令,需要进行两次访存才能取出操作数,首先获取操作数有效地址,然后从该地址取出操作数。因此,这种指令的处理需要包括取指阶段、解码阶段和执行阶段。关于操作数寻址方式的内容,我们在第五章的指令系统中刚刚学习过,当时还请同学们对常见的操作数寻址方式进行过总结。不难发现,间接寻址以及间接寻址加变址寻址、除取指令需要进行一次访存外,还需要额外两次访存才能最终取到操作数。当指令执行完毕后,若出现中断请求,CPU将进入中断响应阶段,保存断点并将中断处理程序入口地址送入程序计数器PC,从而实现当前程序与中断处理程序的切换。

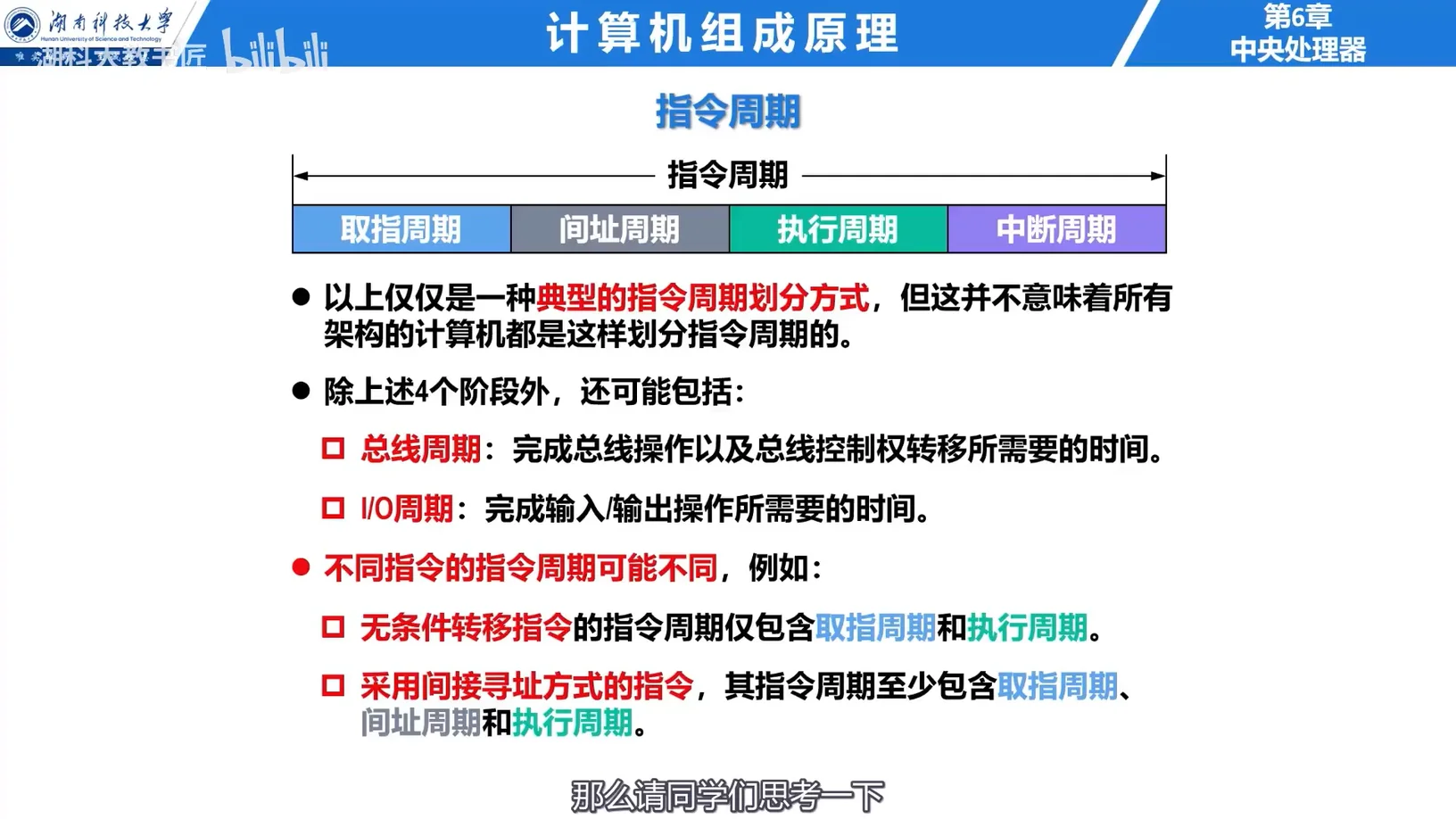

综上所述,一个完整的指令周期包含取指周期、执行周期、中断周期和总线周期四个阶段,例如下图所示。需要指出的是,虽然上述是一种典型的指令周期划分方式,但并非所有架构的计算机都遵循这种划分。除上述四个阶段外,还可能包括完成总线操作以及总线控制权转移所需的总线周期,以及完成输入输出操作所需的IO周期。尽管我们目前还未学习总线和IO的相关知识,但这并不影响当前的理解。

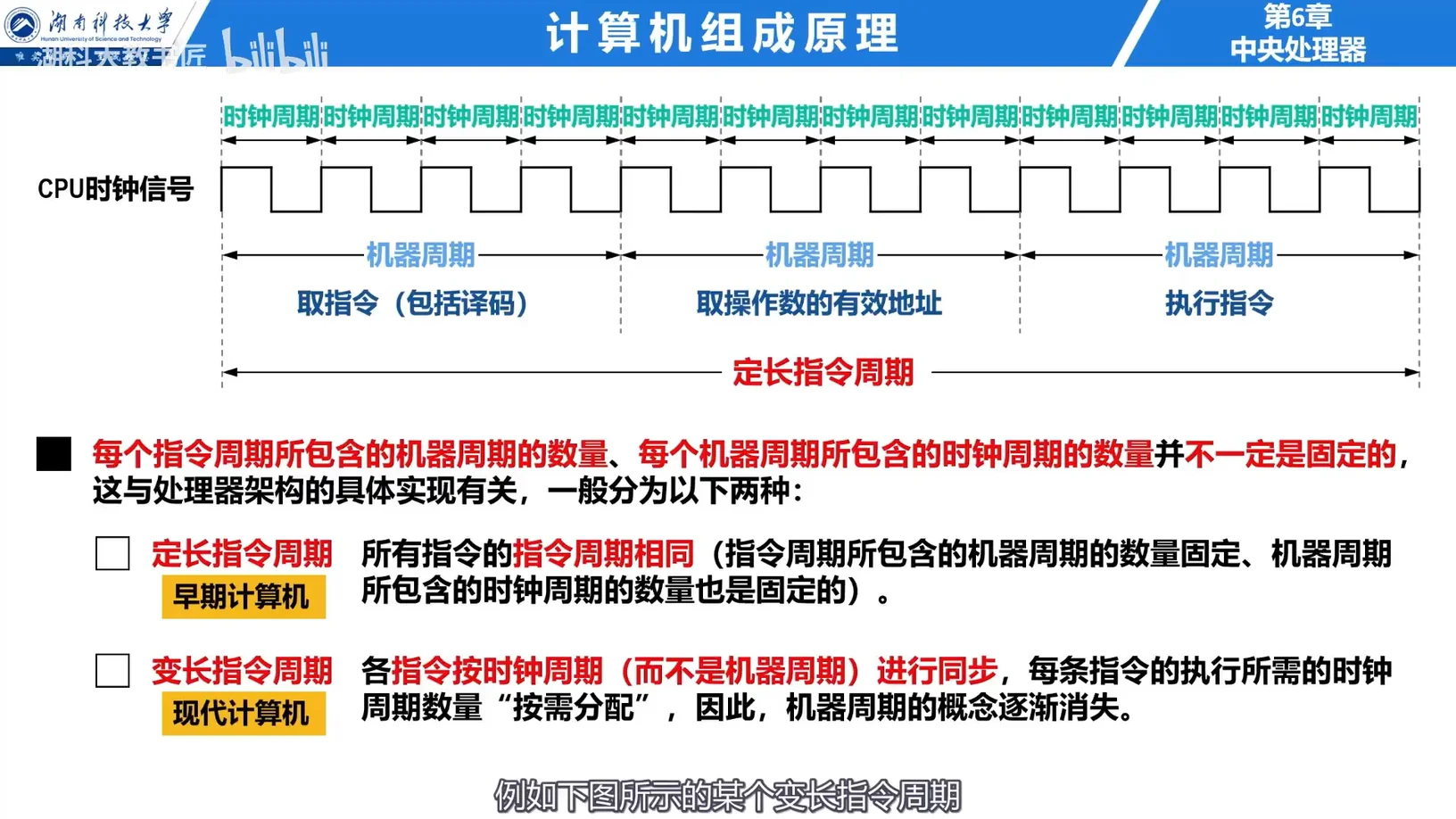

请同学们注意,不同指令的指令周期可能不同。例如,无条件转移指令的指令周期由取指周期和执行周期构成。而对于采用间接寻址方式的指令,其指令周期至少包括取指周期、兼职周期和执行周期。那么,请同学们思考一下,如何表示一个指令周期的具体时长呢?相信同学们已经想到了,那就是利用我们在第一章有关于运算速度相关的性能指标那些特征曾给同学们介绍过的CPU时钟周期,来表示一个指定周期的具体时长。我们来举例说明,这是CPU的时钟信号,它是一种脉冲信号。脉冲信号是周期性出现的,这里的周期称为CPU时钟周期。

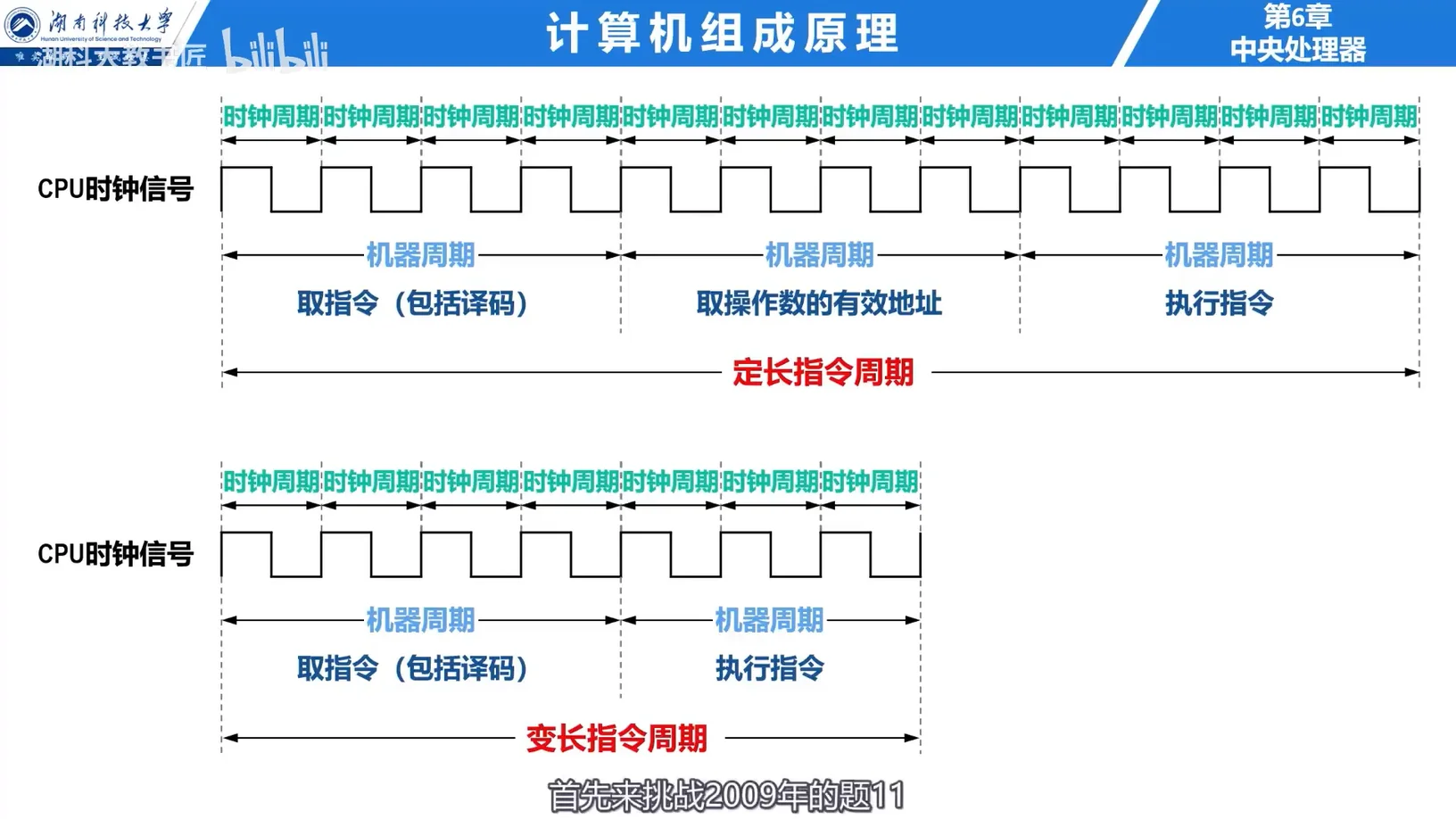

为了便于各指令同步,通常将指令周期划分为多个机器周期。机器周期,一般而言,指的是从主存取出一个存储字所需的最短时间,而每个机器周期又由若干个时钟周期组成。例如,在下图中,每4个CPU时钟周期构成一个机器周期,在这个机器周期阶段完成取指令的任务,在接下来的机器周期完成取操作数有效地址的任务,在再下一个机器周期完成执行指令的任务。因此,一个指令周期由三个机器周期构成,而每个机器周期又由4个CPU时钟周期组成。请同学们注意,不要把思维局限在本地上。

实际上,每个机器周期包含的时钟周期数量并不固定,这取决于处理器架构的具体实现。通常分为两种类型:定长指令周期和变长指令周期。在定长指令周期中,所有指令的指令周期相同,即指定周期内包含的机器周期数量是固定的,因此机器周期中包含的时钟周期数量也是固定的。例如,早期计算机采用的就是定长指令周期。而对于变长指令周期,各指令是按照CPU时钟周期而不是机器周期进行同步的。每条指令的执行所需的时钟周期数量会根据需要分配,因此机器周期的概念逐渐淡化。需要指出的是,现代计算机通常采用变长指令周期。例如,下图显示的某个变长指令周期仅包含两个机器周期,其中一个机器周期包含4个CPU时钟周期,另一个则包含3个CPU时钟周期。

好的,本节课的内容就介绍到这里。接下来,请同学们趁热打铁,挑战两道相关的408考研真题。首先,我们来挑战2009年的真题第11题,请同学们暂停视频,思考一下这个问题,然后给出你的答案。

本题答案为选项C,大家是否都选对了?我们来一起分析一下。这与我们之前讨论的一个例子有关,该例子说明了指令周期的两个阶段:在第一个机器周期内完成取指令操作,而在第二个机器周期内完成取操作数的有效地址。因此,CPU区分指令和数据是基于指令周期的不同阶段。

接下来,我们将挑战2011年的T19题目。针对本题中同学们尚未学习的相关知识点,我们提供了以下提示。请同学们暂停视频播放,稍作思考,然后给出你的答案。

本题答案为选项C,大家是否都选对了?我们来一起分析一下。这与我们之前讨论的一个例子有关,当时我们考虑了不采用指令预取技术的情况。因此,每个指令周期都需要进行取指令操作。例如,在图中所示的情况下,当题目表明不使用指令预取技术时,如果指令字节与存储字节相等且边界对齐,取指令需要访问内存一次;否则,会进行多次访存。因此,选项A的叙述是正确的。这就是我们本节课介绍的定长指令周期与变长指令周期的基本概念。对于定长指令周期,所有指令的指令周期相同,即指令周期包含的机器周期数量固定,而机器周期又包含的固定的时钟周期数量。而对于变长指令周期,各指令按CPU时钟周期同步执行,每条指令所需的时钟周期数量根据需要分配。

综上所述,选项B的叙述是正确的。题目给出的场景是机器处于开中断状态。开中断状态意味着处理器允许接收并响应外部或内部中断请求,能够中断当前的程序执行,以处理更高优先级的任务。在我们上节课介绍的指令执行的基本流程中,也包含了对中断请求的判断和响应环节。

综上所述,选项D的叙述是正确的。通过排除法,我们可以判断选项C的叙述是错误的。请同学们在指令执行流程图中找出选项C叙述错误的原因,相信大家都能找到答案。那就是在取指令时,系统会自动更新程序计数器PC的值,使PC指向下一条指令,以便于后续取指。尽管题目中提到当前的取指令为空操作指令,但BC值仍会自动更新。因此,选项C的叙述是错误的,它就是本题的答案。

本讲,我们将探讨指令周期各阶段的数据流。数据流是指为实现指定功能需要依次访问的数据序列。请同学们注意,在指令周期的不同阶段,需要依次访问的数据序列是不同的。此外,不同指令的数据流也可能各异。通过上节课的学习,我们知道指令周期可划分为取指周期、执行周期、中断周期。

首先分析取指周期的数据流。在该阶段,需要完成从主存中根据程序计数器PC的值取出指令并将其送入指令寄存器IR。在下图的基础上,我们进一步描绘了取指周期的数据流:程序计数器PC的值,即当前指令地址,被送入存储器地址寄存器MAR中,随后通过地址总线传送到主存。接着,控制单元CEO通过控制总线向主存发出读命令,使得PC所指向的主存单元中的内容——即指令,通过数据总线传送到存储器数据寄存器MDR中,并最终进入指令寄存器IR。至此,IR中的内容即为即将执行的指令。随后,控制单元CEO将PC的内容加1,以形成下一条指令的地址。

在探讨兼职周期的数据流时,该阶段的任务是根据指令地址码从主存获取操作数的有效地址。将指令寄存器IR中的内容,即指令的偏移地址部分记作AB,IR送到存储器地址寄存器MAR中,进而可以通过地址总线传送到主存。随后,控制单元CEO通过控制总线向主存发送读命令,使得形式地址所指向的主存单元的内容,即操作数的有效地址,通过数据总线传送到存储器数据寄存器MDR中。这样,MDR中的内容便是操作数的有效地址。而在执行周期,不同指令的操作各异,可能包括CPU内部寄存器间的数据传输、对主存或I/O设备的读写操作,以及算术运算单元ALU的操作。综上所述,执行周期无法用单一的数据流图来描述。

在中断周期阶段,需要完成的任务包括保存断点并将中断服务程序的入口地址送入程序计数器PC。在下图的基础上,我们进一步描绘出中断周期阶段的数据流。在控制单元CEO的控制下,首先进行程序断点的压栈操作,通过减一操作更新堆栈指针SP,以便其指向栈顶。这一减一操作的原因在于我们之前所学的堆栈寻址方式,我们知道栈是向下增长的,也就是向低地址增长,因此需要减一。将SP的内容送入存储器地址寄存器MAR中,进而通过地址总线传送到主存。接着,控制单元CEO通过控制总线向主存发送写命令,并将PC的值,即程序断点,送入存储器数据寄存器MDR中,再通过数据总线存入主存。具体来说,就是将程序断点存入了位于主存中的栈顶。此外,CEO还需将中断服务程序的入口地址送入PC中,以准备下一条指令周期的取指周期。