重要程度:☆☆☆☆☆

知乎排版有点费力,可参考原网页:Notion – The all-in-one workspace for your notes, tasks, wikis, and databases.

Takeaways

- 类比:图书馆 - 外部存储, 书桌 - cache

- 处理器每次请求为一个字

- 为利用空间局部性,cache 的数据块容量应大于一个字。单字的单个数据块的大小是 4 字节,但是通常都会更大(单个数据块多字大小)。

- 要搞清楚地址位数和 cache 位数(容量)的对应关系

- cache 块大小:Data 部分是多少字节,4 字节是单字

一 、cache 读操作

cache miss 带来的疑问:

-

如何知道数据项是否存在于 cache 中?

——根据地址后几位(去掉 offset 字段)找到在 cache 中的位置,然后比较 tag -

如果知道数据项存在于 cache 中,又该如何找到这个数据项?

——找到确定位置,输出 data 部分即可

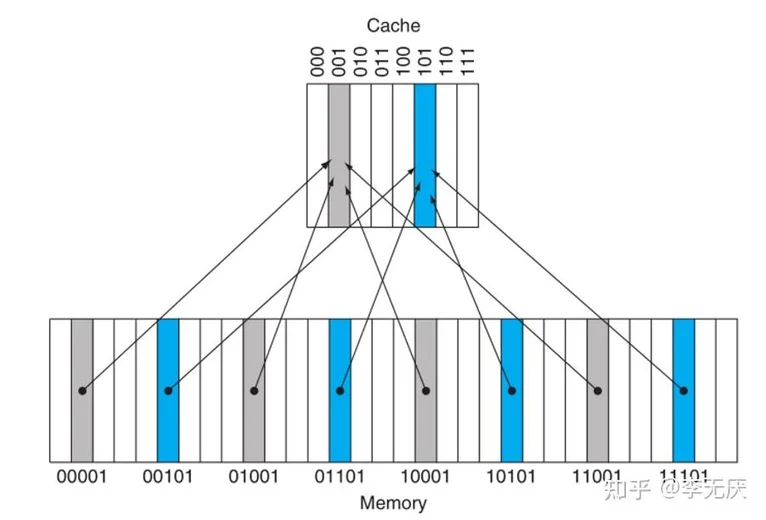

直接映射(direct mapped)

在 cache 中为每个存储中的数据字进行位置分配的最简单方式,就是基于它在存储中的地址来分配 cache 中的位置

公式:

中地址中的数据块数量

-

标签 tag:用来处理映射冲突

标签中只需要保存 Memory 地址的高位部分,便可以区别映射到同一个 Cache 块的数据字 -

有效位 valid:判断 cache 中的数据块中是否保存有效信息

比如刚启动时,cache 中没有有效数据,有效位均为 N,这样标签位都是无意义的

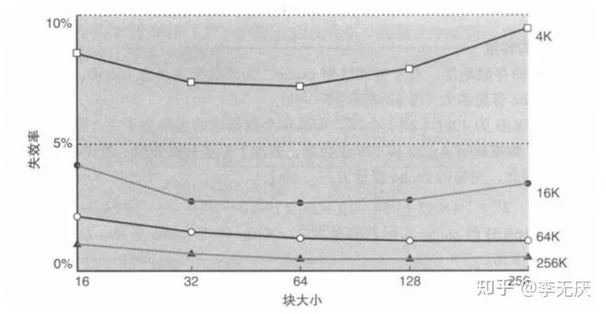

- 标签字段:用来和 cache 中存放数据的标签位进行比较。

- 索引字段:用来选择数据块。

数据字的地址是 4 字节对齐的,每个地址的最低两位用来表示对应的字节地址。因此,如果存储都是字对齐的,那么在访问数据字时地址的最低两位可以忽略不计。

访问 cache 所需的所有数据,是 cache 容量(对应索引)和存储地址大小(对应 tag)的函数。这是因为 cache 中既保存了数据,也保存了标签

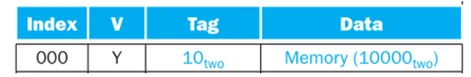

地址按位解析与 cache 容量计算

- cache 大小为

数据块,因此索引字段为 n 位(图中的中间 10 位)。 - 数据块大小为

个单字 ( 字节),因此在单个数据块中使用 m 位来索引单字,使用地址的最低 2 位来索引字节。 - 其余的位数都是 tag 字段:

- 1、0 两位是字节索引

注意:有效位不是地址里的,是算 cache 容量时要加上的

例子:数据块为单字,m=0

如果某数据块的标签与地址的高 52 位相等,同时对应的有效位有效,则该访存请求在 cache 中 hit,处理器所需数据将被读出。否则,出现 cache miss

- 真实容量: 单个数据块容量标签字段大小有效位大小

- 命名容量:cache 命名规范中一般只考虑数据的大小,并不考虑标签和有效位的大小。

- 对于 cache 来说,总容量是用于数据存储的容量的 1.4 倍

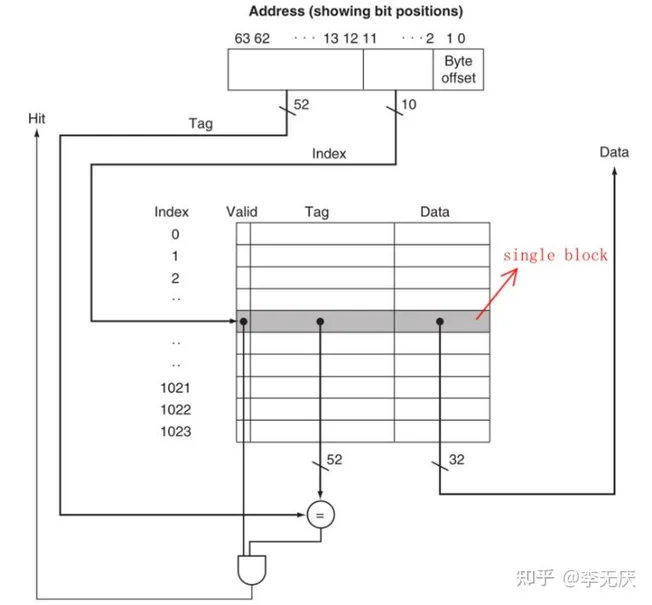

块容量与失效率、性能的关系

-

随着块大小的增长,失效率通常都在下降;

容量更大,更能挖掘空间局部性,更不容易 miss -

但如果相对于 cache 大小,块容量过大,实际上失效率会逐渐上升。

这是因为 cache 中可存放的块数变少了。最终,某个数据块会在它的大量数据被访问之前就被挤出 cache。

增大块容量与性能更多的分析见 P271

cache miss 处理

两个控制器作用,一个是处理器的控制单元,一个是单独的控制器,用来初始化内存访问和重填 cache。

cache 失效将会停顿整个处理器来等待内存 (返回数据), 特别是冻结临时寄存器和程序员可见寄存器的内容。

一旦发生指令 cache 失效,可以定义如下处理步骤:

- 将 PC 的原始值 (当前 PC-4) 发送到内存。

- 对主存进行读操作,等待主存完成本次访问。

- 写 cache 表项,将从内存获得的数据写入到该表项的数据部分,将地址的高位 (来自于 ALU) 写入标签字段,并将有效位置为有效。

- 重启指令执行。这将会重新取指,本次取指将在指令 cache 中命中。

与上述相比,数据访问的 cache 控制本质上是相同的。一旦失效,简单地暂停处理器,直到内存返回数据。

二、cache 写操作(策略)

write through 和 write-back 是策略,write buffer 是种优化结构

write through(写穿透 / 写直达)

为保持 cache 和主存一致,在存储指令执行将数据写入 cache 的同时写入主存。

写操作的另一个关键点是写失效的处理。先从主存中取来对应数据块中的数据,之后将其写入 cache 中,覆盖引发失效的数据块中的数据。同时,也会使用完整地址将数据写回主存。

缺点

每次的写操作都会引起写主存的操作。这些写操作延时很长,至少 100 个处理器时钟周期,这会 大大降低处理器的性能。

write buffer(写缓冲)

放一边去慢慢写,你写你的,我 CPU 执行我的

write buffer 是一个保存等待写入主存的数据的队列。数据写入 cache 的同时也写入写缓冲(器)中,之后处理器继续执行。当写入主存的操作完成后,写缓冲中的 entry 将被释放。

缺点

写缓冲满了,处理器流水线必须停顿直到写缓冲中出现空闲 entry;当写操作 occur in bursts 时,容易导致写操作的产生速度快于主存系统的处理速度,产生停顿。

write-back(写返回)

先不写,非要我写了我再写

当发生写操作时,新值只被写入 cache 中,被改写的数据块在替换出 cache 时才被写到下一级存储。

缺点

写返回策略的实现比写穿透策略要复杂得多。