题7

题目

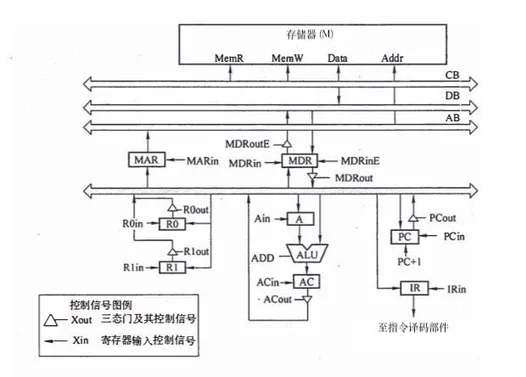

【2009统考真题】某计算机字长 16 位,采用 16 位定长指令字结构,部分数据通路结构如下图所示(见下页),图中所有控制信号为 1 时表示有效、为 0 时表示无效,例如控制信号 MDRinE 为 1 表示允许数据从 DB 打入 MDR,MDRin 为 1 表示允许数据从内总线打入 MDR。假设 MAR 的输出一直处于使能状态。加法指令 “ADD (R1),R0” 的功能为(R0)+((R1))→(R1),即将 R0 中的数据与 R1 的内容所指主存单元的数据相加,并将结果送入 R1 的内容所指主存单元中保存。

下表给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

分析

题干已给出取值和译码阶段每个节拍的功能和有效控制信号,我们应以了解取指阶段中数据通路的信息流动为突破口,读懂每个节拍的功能和有效控制信号,然后应用到解题思路中,包括划分执行步骤、确定完成的功能、需要的控制信号。

先分析题干中提供的示例(本部分解题时不做要求):

取指令的功能是根据PC的内容所指的主存地址,取出指令代码,经过MDR,最终送至IR。这部分和后面的指令执行阶段的取操作数、存运算结果的方法是相通的。

在读/写存储器前,必须先将地址(这里为(PC))送至MAR。

读/写的数据必须经过MDR,指令取出后PC自增1。

然后将读到的MDR中的指令代码送至IR进行后续操作。

指令“ADD (R1), R0”的操作数一个在主存中,一个在寄存器中,运算结果在主存中。根据指令功能,要读出R1的内容所指的主存单元,必须先将R1的内容送至MAR,即

因此,将R1的内容所指的主存单元的数据读出到MDR的节拍安排如下:

ALU一端是寄存器A,MDR或R0中必须有一个先写入A中,如MDR。

然后执行加法操作,并将结果送入寄存器AC。

之后将加法结果写回到R1的内容所指的主存单元,注意MAR中的内容没有改变。

有效控制信号的安排并不难,只需看数据是流入还是流出,如流入寄存器X就是Xin,流出寄存器X就是Xout。还需注意其他特殊控制信号,如

于是得到参考答案如下表所示。

| 时钟 | 功能 | 有效控制信号 |

|---|---|---|

| C5 | MAR | R1out, MARin |

| C6 | MDR | MemR, MDRinE |

| C7 | A | MDRout, Ain |

| C8 | AC | R0out, ADD, ACin |

| C9 | MDR | ACout, MDRin |

| C10 | M(MAR) | MDRoutE, MemW |

(续表)

本题答案不唯一,若在C6执行M(MAR)

| 时钟 | 功能 | 有效控制信号 |

|---|---|---|

| C5 | MAR | R1out, MARin |

| C6 | MDR | MemR, MDRinE, R0out, Ain |

| C7 | AC | MDRout, ADD, ACin |

| C8 | MDR | ACout, MDRin |

| C9 | M(MAR) | MDRoutE, MemW |